Kasdienybėje mes susiduriame su įvairių tipų elektroninėmis programėlėmis. Viena iš elektronikos gamybos revoliuciją sukėlusių technologijų yra „ Integrinis grandynas “. Ši technologija sumažino elektroninių gaminių dydį, padidindama loginiai vartai už lustą. Šiandien mes turime skirtingus IC tipus ir konfigūracijas. Stebėdami aplinkui pastebime, kad kai kurie IC gali būti naudojami tik vienai konkrečiai programai, o kai kurie IC gali būti perprogramuojami ir naudojami įvairioms programoms. Šie IC tipai vadinami ASIC. Bet kuo jie skiriasi? Kaip įmanoma juos perprogramuoti? Kodėl kai kurių IC negalima perprogramuoti? Tikėkitės, kad rastumėte atsakymus į šiuos klausimus.

Kas yra ASIC (konkrečios programos integruotasis grandynas)?

ASIC pilna forma yra Programai būdingas integruotasis grandynas. Šios grandinės yra pritaikytos pagal paskirtį, t. specialiai pritaikyti IC tam tikrai programai. Paprastai jie kuriami nuo šaknies lygio, atsižvelgiant į konkrečios programos reikalavimus. Kai kurie iš pagrindinių konkrečios programos integruotų grandinių pavyzdžiai yra lustai, naudojami žaisluose, lustai, naudojami sąsajai su atmintimi ir mikroprocesoriais, ir tt ... Šie lustai gali būti naudojami tik tam tikslui, kuriam jie yra skirti. Tikėtina, kad šie IC tipai pirmenybė teikiama tik tiems produktams, kurių gamybos procesas yra didelis. Kadangi ASIC yra suprojektuoti nuo pagrindinio lygio, jie turi didelę kainą ir yra rekomenduojami tik didelės apimties kūriniams.

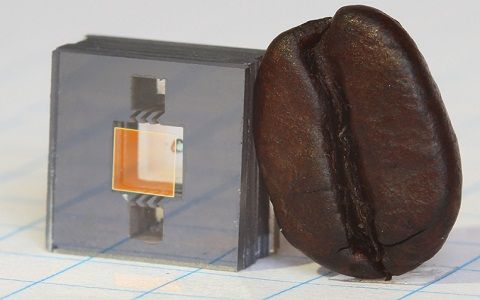

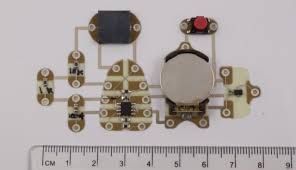

Pagrindinis ASIC privalumas yra sumažintas lusto dydis, nes per vieną lustą sukonstruotas didelis skaičius funkcinių grandinės vienetų. Šiuolaikiniame ASIC paprastai yra 32 bitų mikroprocesorius , atminties blokai, tinklo grandinės ir tt ... Toks ASIC tipas yra žinomas kaip Lusto sistema . Tobulėjant gamybos technologijoms ir intensyviau tiriant projektavimo metodus, kuriami skirtingo pritaikymo lygio ASIC.

ASIC tipai

ASIC skirstomi į kategorijas pagal pritaikymo kiekį, kurį programuotojui leidžiama atlikti mikroschemoje.

ASIC tipai

Visiškas užsakymas

Šio tipo konstrukcijoje visos loginės ląstelės yra pritaikytos konkrečiam pritaikymui. dizaineris turi specialiai sukurti loginių elementų grandinėms. Visi tinklų sujungimo kaukės sluoksniai yra pritaikyti. Taigi programuotojas negali pakeisti lusto jungčių ir programuodamas turi žinoti grandinės išdėstymą.

Vienas geriausių „Full Custom ASIC“ pavyzdžių yra mikroprocesorius. Šio tipo pritaikymas leidžia projektuotojams pastatyti įvairias analogines grandines, optimizuotas atminties ląsteles ar mechanines struktūras viename IC. Šis ASIC yra brangus ir užima daug laiko gaminant ir projektuojant. Šių IC projektavimas užtrunka apie aštuonias savaites.

Paprastai jie skirti aukšto lygio programoms. Didžiausias našumas, sumažinta sritis ir didžiausias lankstumas yra pagrindinės „Custom“ dizaino savybės. Galų gale, rizika yra didelė, nes loginiai elementai, rezistorius ir tt ... naudojami grandinės elementai nėra iš anksto išbandyti.

Pusiau pritaikytas

Šio tipo dizaino logikos langeliai yra paimti iš standartinių bibliotekų. jie nėra rankų darbo, kaip ir „Custom Custom Design“. Kai kurios kaukės yra pritaikytos, o kai kurios paimamos iš anksto sukurtos bibliotekos. Remiantis logikos langelių, paimtų iš bibliotekos, tipu ir tinkamumo, kurį leidžiama sujungti, kiekiu, šie ASIC yra suskirstyti į du tipus - standartinį ląstelių pagrindu veikiantį ASIC ir „Gate Array“ pagrįstą ASIC.

1). Standartinis ląstelių pagrindu veikiantis ASIC

Norėdami žinoti šias IC, pirmiausia supraskime, ką reiškia standartinė ląstelių biblioteka. Kai kurios loginės ląstelės, tokios kaip IR vartai, ARBA vartai , multipleksoriai, šlepetės yra iš anksto suprojektuoti dizainerių, naudojant skirtingas konfigūracijas, standartizuoti ir saugomi bibliotekos pavidalu. Ši kolekcija yra žinoma kaip standartinė ląstelių biblioteka.

Standartinis ląstelių pagrindu veikiantis ASIC

Standartinėse ląstelėse naudojamos ASIC loginės ląstelės iš šių standartinių bibliotekų. ASIC luste standartinis langelio plotas arba lankstus blokas sudarytas iš standartinių langelių, išdėstytų eilučių pavidalu. Kartu su šiais lanksčiais blokais mikroschemos, tokios kaip mikrovaldikliai ar net mikroprocesoriai, naudojamos mikroschemoje. Šios mega ląstelės taip pat žinomos kaip „Mega“ funkcijos, sistemos lygio makrokomandos, fiksuoti blokai, funkciniai standartiniai blokai.

Aukščiau pateiktame paveiksle pavaizduotas standartinis langelio ASIC su vienu standartiniu langelio plotu ir keturiais fiksuotais blokais. Kaukių sluoksniai pritaikomi. Čia dizaineris gali įdėti standartines langelius bet kur ant štampo. Tai taip pat žinoma kaip C-BIC.

2). Vartų masyvo pagrindu veikiantis ASIC

Šio tipo pusiau pritaikyti ASIC iš anksto apibrėžti tranzistoriai ant silicio plokštelės .t. dizaineris negali pakeisti ant tranzistorių esančių tranzistorių. Bazinis masyvas yra iš anksto nustatytas vartų masyvo modelis, o bazinė ląstelė yra mažiausia pasikartojanti bazinio masyvo ląstelė.

Projektuotojas yra atsakingas tik už tranzistorių jungčių keitimą naudojant pirmuosius kelis metalinius štampo sluoksnius. Dizaineris renkasi iš vartų masyvo bibliotekos. Jie dažnai vadinami „Masked Gate Array“. Vartų masyvo ASIC yra trijų tipų. Jie yra „Channeled Gate Array“, „Channel mažiau“ vartų masyvas ir struktūrizuotas vartų masyvas.

a). Kanalų vartų masyvas

Šio tipo vartų matricoje tarp tranzistorių eilučių paliekama vieta laidams. Jie yra panašūs į CBIC, nes paliekama vietos tarpusavio ryšiui tarp blokų, tačiau kanalų vartų masyvo ląstelių eilutės yra fiksuotos aukščio, o CBIC šią erdvę galima koreguoti.

Kanalų vartų masyvas

Kai kurios pagrindinės šio vartų masyvo savybės yra šios: vartų masyvas naudoja iš anksto nustatytus tarpus tarp eilučių tarpusavio ryšiui. Gamybos laikas yra nuo dviejų dienų iki dviejų savaičių.

b). Kanalo mažiau vartų masyvas

Maršrutui tarp langelių eilučių nelieka laisvos vietos, kaip matyti kanalizuotų vartų masyve. Čia maršrutas atliekamas iš viršaus vartų masyvo ląstelių, nes mes galime pritaikyti ryšį tarp metalo 1 ir tranzistorių. Maršrutavimui paliekame nenaudojamus tranzistorius, esančius maršruto kelyje. Gamybos laikas yra apie dvi savaites.

Kanalo mažiau vartų masyvas

c). Struktūrinis vartų masyvas

Šio tipo vartų masyvas turi įterptą bloką kartu su vartų masyvo eilutėmis, kaip parodyta aukščiau. Struktūrinis vartų masyvas turi didesnį CBIC ploto efektyvumą. Kaip ir „Masked gate“ masyvas, jų kaina yra mažesnė ir greitesnis. Čia fiksuotas įterptosios funkcijos dydis apriboja struktūrizuotų vartų masyvą. Pavyzdžiui, ar šiame vartų masyve yra sritis, rezervuota 32 k bitų valdikliui, bet jei programoje reikalaujame tik 16 k bitų valdiklio srities, likusi sritis bus švaistoma. Visų vartų masyvo trukmė yra nuo dviejų dienų iki dviejų savaičių ir visi turi pritaikytą ryšį.

Struktūrinis vartų masyvas

Programuojamas ASIC

Yra dviejų tipų programuojami ASIC. Jie yra PLD ir FPGA

PLD (programuojami loginiai įrenginiai)

Tai yra lengvai pasiekiamos standartinės ląstelės. Mes galime užprogramuoti PLD pritaikyti dalį programos, todėl jie laikomi ASIC. PLD programavimui galime naudoti skirtingus metodus ir programinę įrangą. Juose yra įprasta loginių langelių matrica, paprastai programuojama masyvo logika kartu su šlepetėmis ar skląsčiais. Čia sujungimai yra vienas didelis blokas.

PROM yra įprastas šio IC pavyzdys. EPROM naudoja MOS tranzistorius kaip jungiamuosius elementus, todėl pritaikydami aukštą įtampą galime jį užprogramuoti. PLD neturi pritaikytų loginių elementų ir nesusiję. Jie turi greitą dizaino posūkį.

Programuojami loginiai įrenginiai

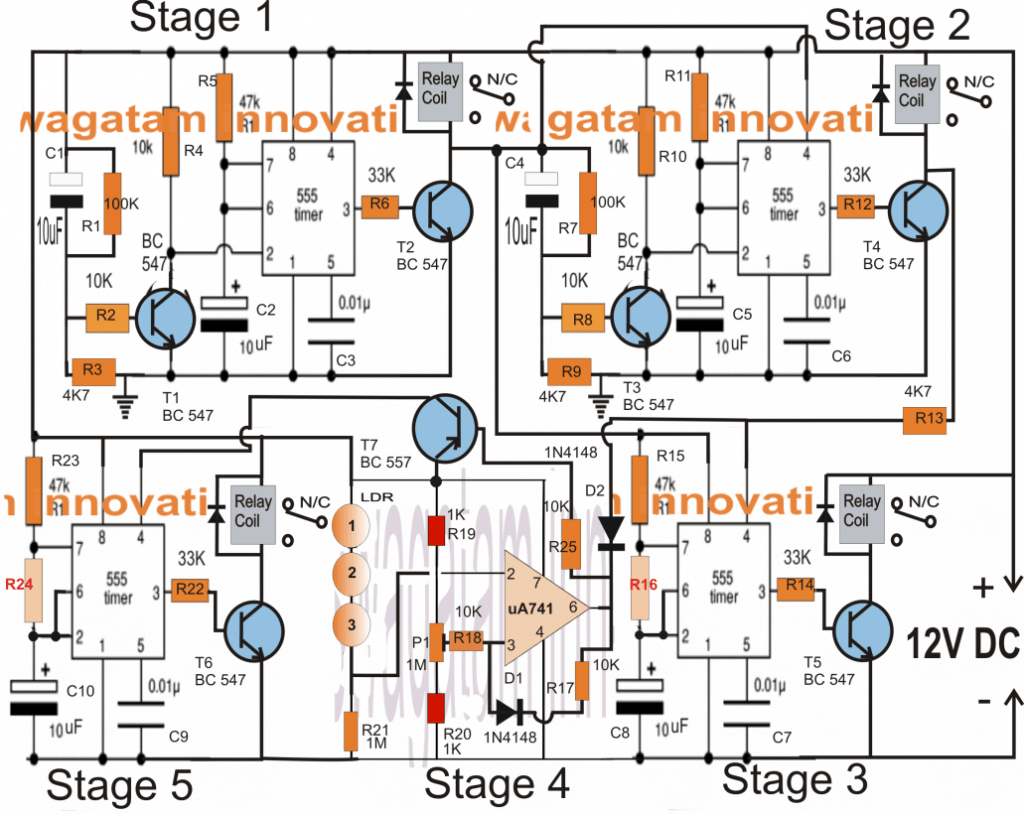

FPGA (lauko programuojamas vartų masyvas)

Kur PLD turi programuojamą masyvo logiką kaip loginius langelius FPGA turi panašų į vartų masyvą išdėstymą. PLD yra mažesni ir mažiau sudėtingi nei FPGA. Dėl savo lankstumo ir savybių FPGA keičia TTL mikroelektroninėse sistemose. Projektavimo laikotarpis yra tik kelios valandos.

Lauke programuojamas vartų masyvas

Šerdį sudaro programuojamos pagrindinės loginės ląstelės, galinčios atlikti abu veiksmus kombinacinis ir nuosekli logika . Mes galime programuoti loginius langelius ir susieti tarpusavyje, naudodami kai kuriuos metodus. Pagrindines logines ląsteles supa programuojamų jungčių matrica, o šerdį - programuojamos įvesties / išvesties ląstelės.

FPGA paprastai susideda iš konfigūruojamų loginių blokų, konfigūruojamų įvesties / išvesties blokų, programuojamų jungčių, laikrodžio schemų, ALU, atminties, dekoderių.

Mes matėme skirtingus ASIC tipus. Dabar supraskime, kada visi šie pritaikymai ir sujungimai atliekami gamybos metu.

Konkrečios programos integruotų grandinių (ASIC) projektavimo srautas

ASIC projektavimas atliekamas palaipsniui. Ši žingsnių tvarka yra žinoma kaip ASIC dizainas Srautas. Projektavimo srauto žingsniai pateikti žemiau esančioje schemoje.

ASIC dizaino srautas

Dizaino įrašas: Šiame etape projekto mikroarchitektūra įgyvendinama naudojant aparatūros aprašymo kalbas, tokias kaip VHDL, „Verilog“ ir „System Verilog“.

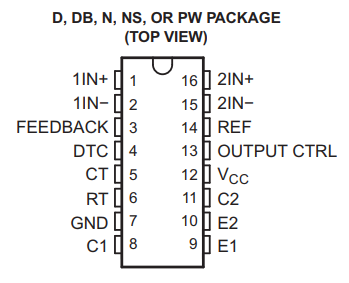

Logikos sintezė: Šiame etape sudaromas tinkamų naudoti loginių elementų, sujungimų tipų ir visų kitų dalių, reikalingų programai, sąrašas naudojant DTL.

Sistemos skaidymas: Šiame žingsnyje mes padalijame daugiausia dydžio štampą į ASIC dydžio gabalus.

Išankstinio maketo modeliavimas: Šiame etape atliekamas modeliavimo testas, siekiant patikrinti, ar projekte nėra klaidų.

Grindų planavimas: Šiame etape lustuose yra išdėstyti netlist blokai.

Vieta: Šiame etape nustatoma ląstelių vieta bloko viduje.

Maršrutas: Šiame etape nustatomi ryšiai tarp blokų ir langelių. Ekstrahavimas: Šiame etape mes nustatome elektrines savybes, tokias kaip varžos vertė ir jungties talpos vertė.

Modeliavimas po išdėstymo: Prieš pateikiant modelį gamybai, šis modeliavimas atliekamas siekiant patikrinti, ar sistema tinkamai veikia kartu su jungtimi.

ASIC pavyzdžiai

Žinodami skirtingas ASIC charakteristikas, dabar pamatykime keletą ASIC pavyzdžių.

Standartinis langelių pagrindu veikiantis ASIC: LCB 300k, 500k iš „LSI Logic Company“, SIG1, 2, 3 šeimos iš „ABB Hafo Inc.“, „GCS Plessey“ GCS90K.

„Gate Array“ produktai: AUA20K iš „Harris Semiconductor“, SCX6Bxx iš „National Semiconductors“, TGC / TEC šeimos iš „Texas Instruments“.

PLD produktai: „Advanced Micro Devices“ PAL šeima, „Philips Semiconductors“ GAL šeima, „XILINX“ - XC7300 ir EPLD.

FPGA produktai: „XILINX“ serijos „XC2000“, „XC3000“, „XC4000“, „XC5000“, „QuickLogic“ pASIC1, „Altera“ - MAX5000.

ASIC programos

ASIC unikalumas pakeitė elektronikos gamybos būdą. Tai sumažino štampų dydį, tuo pačiu padidindami loginiai vartai už lustą. ASIC dažniausiai teikiama pirmenybė aukšto lygio programoms. ASIC lustas naudojamas kaip IP branduoliai palydovams, ROM gamybai, Mikrovaldiklis įvairių rūšių taikymas medicinos ir mokslinių tyrimų sektoriuose. Viena iš populiariausių ASIC programų yra „BITCOIN MINER“.

„Bitcoin Miner“

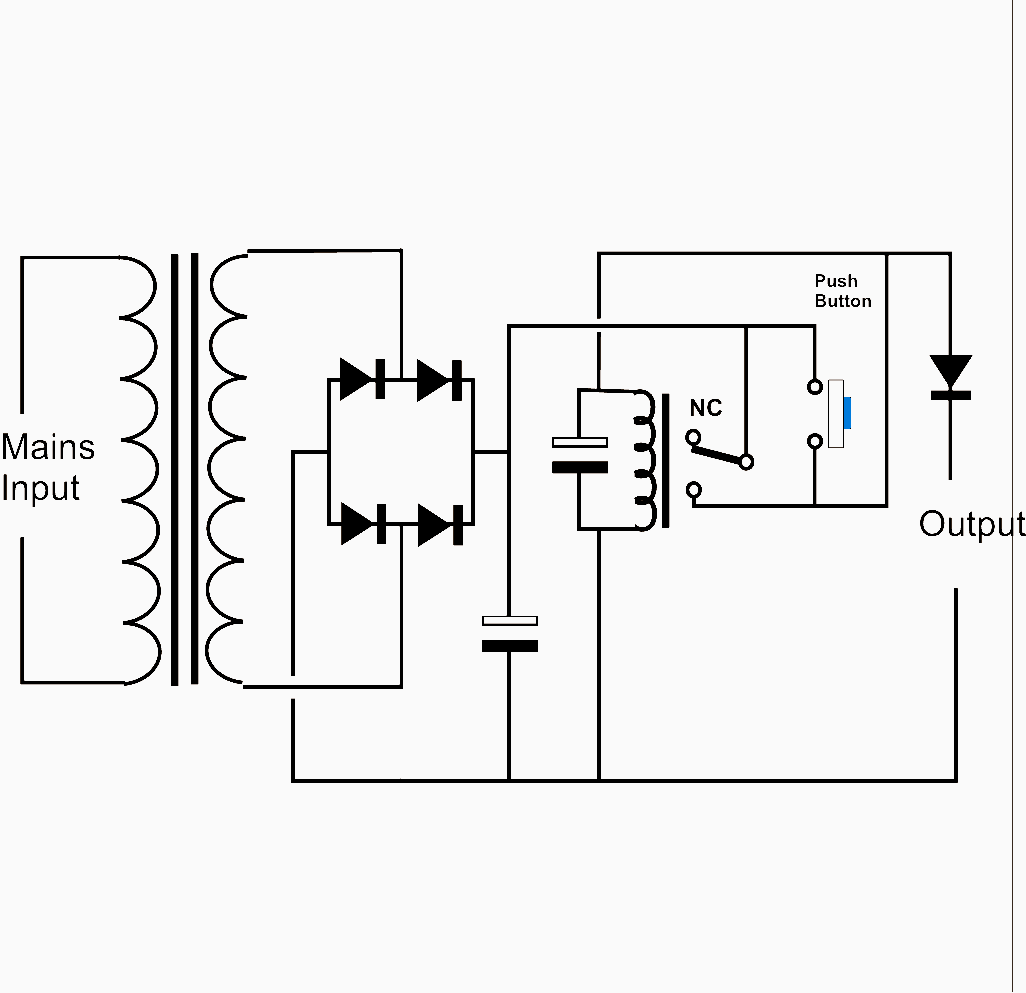

Kriptovaliutos kasyba reikalauja didesnės galios ir didelės spartos aparatūros. Bendrosios paskirties procesorius negali užtikrinti tokios didesnės skaičiavimo galios dideliu greičiu. ASIC bitcoin miners yra lustai, įmontuoti į specialiai sukurtas pagrindines plokštes ir maitinimo šaltiniai , sukonstruotas į vieną vienetą. Tai yra specialiai suprojektuota aparatūra iki bitų kasybos bitų lygio. Šie vienetai gali vykdyti tik vienos kriptovaliutos algoritmą. Tikriausiai kitokio tipo kriptovaliutai reikalingas kitas kalnakasis.

ASIC privalumai ir trūkumai

The privalumai įtraukti šiuos dalykus.

- Mažas ASIC dydis leidžia rinktis sudėtingas didesnes sistemas.

- Kadangi per vieną lustą sukurta daug grandinių, tai sukelia greitaeigius pritaikymus.

- ASIC suvartoja mažai energijos.

- Kadangi jos yra lusto sistema, grandinės yra šalia. Taigi, norint sujungti įvairias grandines, reikalingas labai minimalus maršrutas.

- ASIC neturi problemų dėl laiko ir konfigūracijos po gamybos.

The ASIC trūkumai įtraukti šiuos dalykus.

- Kadangi tai yra pritaikyti lustai, jie suteikia mažai lankstumo programuojant.

- Kadangi šie lustai turi būti suprojektuoti nuo šaknies lygio, jie kainuoja brangiai už vienetą.

- ASIC turi didesnį laiką iki rinkos maržos.

ASIC vs FPGA

ASIC ir FPGA skirtumas apima šiuos dalykus.

ASIC | FPGA |

| Negalima perprogramuoti | Perprogramuojamas |

| Pirmenybė teikiama didelės apimties pastatymams | Pirmenybė teikiama mažos apimties produkcijai |

| Tai yra konkretūs pritaikymai | Naudojamas kaip sistemos prototipai |

| Efektyviam energijos naudojimui reikia mažiau energijos | Mažiau energijos vartojimo reikalauja daugiau energijos |

| Tai yra nuolatinė schema, kurios laikas nuo laiko negalima atnaujinti. | Labai tinka toms programoms, kuriose grandinė turi būti kartkartėmis atnaujinama, tokioms kaip mobiliojo telefono lustai, bazinės stotys ir kt |

Taigi visa tai yra apžvalga Programai būdingas integruotasis grandynas . ASIC išradimas sukėlė milžinišką elektronikos naudojimo būdo pasikeitimą. ASIC kasdieniame gyvenime naudojame įvairių programų forma. Su kuriomis ASIC programomis susidūrėte? Su kokiu ASIC tipu dirbote?