Norint vykdyti kompiuterinę programą, reikia, kad sinchroniškai veiktų daugiau nei vienas kompiuterio komponentas. Pavyzdžiui, Procesoriai - reikalingos valdymo informacijos, adresų ir kt., Magistralių teikimas - informacijai ir duomenims perduoti į atmintį ir iš jos į įvesties / išvesties įrenginius ir pan. Įdomus sistemos faktorius būtų tai, kaip ji tvarko informacijos perdavimą tarp procesoriaus, atminties ir įvesties / išvesties įrenginių. Paprastai procesoriai kontroliuoja visą duomenų perdavimo procesą nuo pat perdavimo pradžios iki duomenų saugojimo paskirties vietoje. Tai padidina procesoriaus apkrovą ir dažniausiai lieka idealioje būsenoje, taip sumažinant sistemos efektyvumą. Norėdami pagreitinti duomenų perdavimą tarp įvesties / išvesties įrenginių ir atminties, DMA valdiklis veikia kaip stoties valdytojas. DMA valdiklis perduoda duomenis su minimaliu procesoriaus įsikišimu.

Kas yra DMA valdiklis?

Terminas DMA reiškia tiesioginę prieigą prie atminties. Aparatas, naudojamas tiesioginei prieigai prie atminties, vadinamas DMA valdikliu. DMA valdiklis yra valdymo blokas , įvesties / išvesties įrenginio dalis sąsajos grandinė , kuris gali perduoti duomenų blokus tarp įvesties / išvesties įrenginių ir pagrindinės atminties su minimaliu procesoriaus įsikišimu.

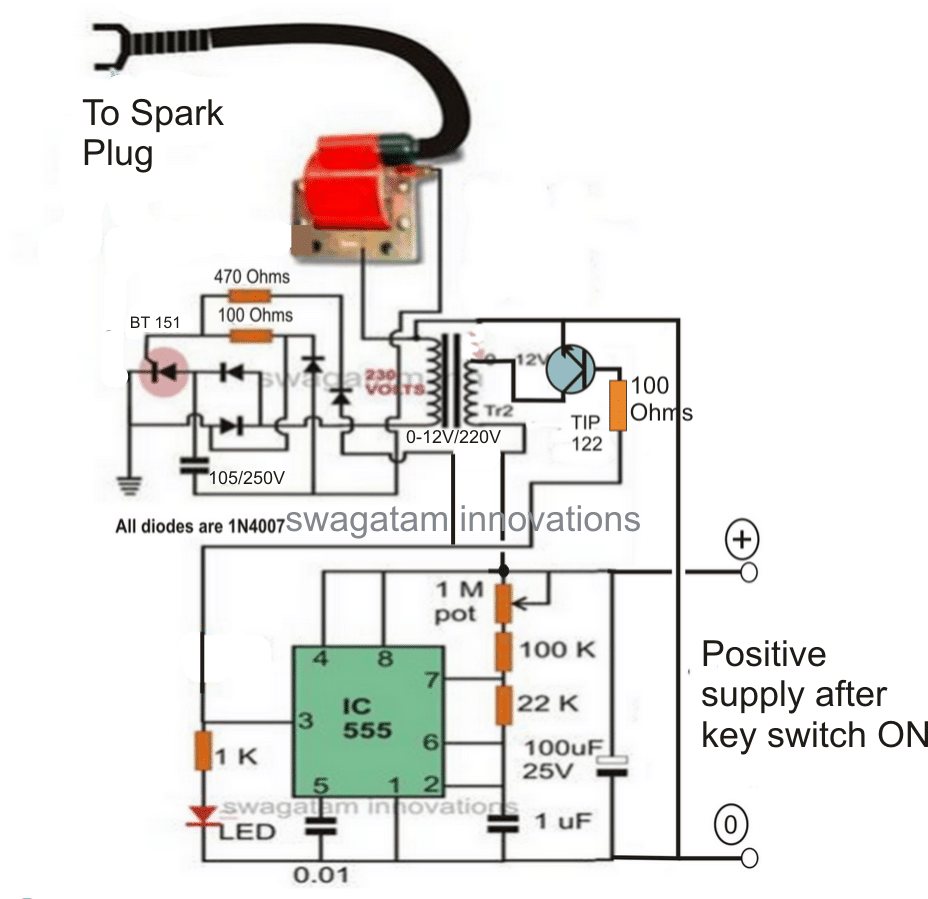

DMA valdiklio schema kompiuterių architektūroje

DMA valdiklis suteikia sąsają tarp magistralės ir įvesties-išvesties įrenginių. Nors jis perduoda duomenis be procesoriaus įsikišimo, jį kontroliuoja procesorius. Procesorius inicijuoja DMA valdiklį išsiųsdamas pradinį adresą, žodžių skaičių duomenų bloke ir duomenų perdavimo kryptį. T. iš įvesties / išvesties įrenginių į atmintį arba iš pagrindinės atminties į įvesties / išvesties įrenginius. Prie DMA valdiklio galima prijungti daugiau nei vieną išorinį įrenginį.

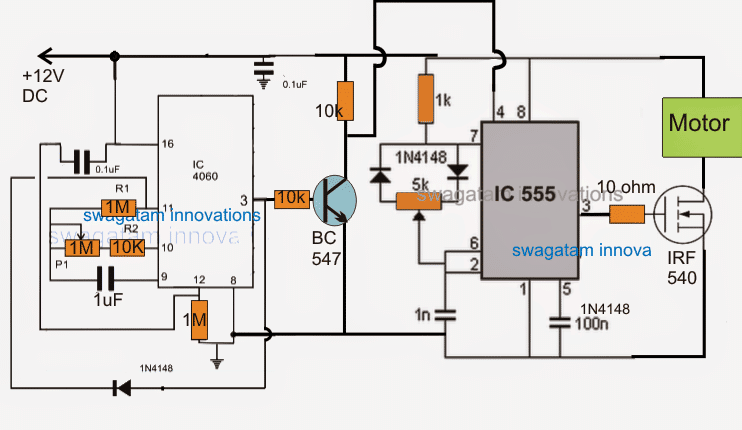

DMA kompiuterių architektūroje

DMA valdiklyje yra adresų blokas, skirtas generuoti adresus ir pasirinkti I / O įrenginį perdavimui. Jame taip pat yra valdymo blokas ir duomenų skaičius, kad būtų galima laikyti perduotų blokų skaičių ir nurodyti duomenų perdavimo kryptį. Kai perkėlimas bus baigtas, DMA praneša procesoriui iškeldama pertrauką. Tipinė DMA valdiklio blokinė schema parodyta žemiau esančiame paveikslėlyje.

Tipinė DMA valdiklio blokinė schema

DMA valdiklio darbas

DMA valdiklis turi dalytis magistrale su procesoriumi, kad galėtų perduoti duomenis. Įrenginys, laikantis magistralę tam tikru laiku, vadinamas magistralės magistralu. Kai reikia perkelti iš įvesties / išvesties įrenginio į atmintį arba atvirkščiai, procesorius sustabdo dabartinės programos vykdymą, didindamas programa skaitiklis, perkelia duomenis per kaminą, tada siunčia DMA pasirinkimo signalą DMA valdikliui per adreso magistralę.

Jei DMA valdiklis yra laisvas, jis reikalauja procesoriaus valdyti magistralę, pakeldamas magistralės užklausos signalą. Procesorius suteikia magistralę valdikliui pakeldamas magistralės suteikimo signalą, dabar magistralės magistras yra DMA valdiklis. Procesorius inicijuoja DMA valdiklį siųsdamas atminties adresus, perduotinų duomenų blokų skaičių ir duomenų perdavimo kryptį. Priskyręs duomenų perdavimo užduotį DMA valdikliui, užuot idealiai laukęs, kol bus baigtas duomenų perdavimas, procesorius atnaujina programos vykdymą, gavęs instrukcijas iš rietuvės.

DMA perdavimas kompiuteriu DMA valdikliu

DMA valdiklis dabar gali visiškai valdyti magistrales ir gali tiesiogiai sąveikauti su atmintimi ir įvesties / išvesties įrenginiais nepriklausomai nuo procesoriaus. Jis perduoda duomenis pagal procesoriaus gautas valdymo instrukcijas. Baigus duomenų perdavimą, jis išjungia magistralės užklausos signalą, o centrinis procesorius išjungia magistralės suteikimo signalą, taip perkeldamas magistralių valdymą į centrinį procesorių.

Kai įvesties / išvesties įrenginys nori inicijuoti perdavimą, jis siunčia DMA užklausos signalą DMA valdikliui, kurį valdiklis patvirtina, jei jis yra laisvas. Tada valdiklis paprašo procesoriaus magistralės, pakeldamas magistralės užklausos signalą. Gavęs magistralės suteikimo signalą, jis perduoda duomenis iš įrenginio. N kanalizuotam DMA valdikliui galima prijungti n išorinių įrenginių.

DMA duomenis perduoda trimis režimais, kurie apima:

iki) „Burst“ režimas : Šiuo režimu DMA perduoda magistrales į procesorių tik užbaigus visą duomenų perdavimą. Tuo tarpu, jei procesoriui reikalinga magistralė, jis turi išlikti idealus ir laukti duomenų perdavimo.

b) Ciklo vagystės režimas : Šiame režime DMA suteikia magistralių valdymą procesoriui po kiekvieno baito perdavimo. Jis nuolat pateikia užklausą dėl magistralės valdymo, perkelia vieną baitą ir grąžina magistralę. Šio procesoriaus nereikia ilgai laukti, jei jam reikalinga magistralė aukštesnio prioriteto užduotims atlikti.

c) Skaidrus režimas: Čia DMA duomenis perduoda tik tada, kai procesorius vykdo instrukciją, kuriai nereikia naudoti magistralių.

8237 DMA valdiklis

- 8237 turi 4 įvesties / išvesties kanalus kartu su lankstumu didinant kanalų skaičių.

- Kiekvieną kanalą galima programuoti atskirai, jis turi 64 tūkst. Adresų ir duomenų galimybes.

- Laiko valdymo blokas, Programos komandos valdymo blokas, Prioriteto kodavimo blokas yra trys pagrindiniai 8237A blokai.

- Vidinius laiko ir išorinio valdymo signalus valdo laiko valdymo blokas.

- Įvairias komandas, kurias mikroprocesorius pateikia DMA, iššifruoja programos komandų valdymo blokas.

- Kuriam kanalui turi būti suteiktas didžiausias prioritetas, nusprendžia prioritetas kodavimo blokas .

8237A turi 27 vidinius registrus.

8237A veikia dviem ciklais - idealus ciklas ir aktyvus ciklas, kur kiekviename cikle yra 7 atskiros būsenos, sudarytos iš kiekvieno laikrodžio periodo.

S0- Pirmoji būsena, kai valdiklis paprašė magistralės ir laukia patvirtinimo iš procesoriaus.

S1, S2, S3, S4 vadinamos darbinėmis 8237A būsenomis, kuriose vyksta faktinis duomenų perdavimas. Jei reikia daugiau laiko perdavimo laukimo būsenoms, tarp šių būsenų pridedama SW.

Norint perkelti iš atminties į atmintį, reikia perskaityti iš atminties ir įrašyti į atmintį. Norint perkelti vieną kartą, reikia aštuonių būsenų. Pirmosios keturios būsenos su S11, S12, S13, S14 abonementais perkelia skaitymą iš atminties, o kitos keturios S21, S22, S23, S24 yra skirtos įrašymui į atmintį.

DMA pereina į idealią būseną, kai nė vienas kanalas neprašo paslaugos ir neatlieka SI būsenos. SI yra neaktyvi būsena, kai DMA yra neaktyvi, kol negauna užklausos. Šioje būsenoje DMA yra programos būsenoje, kur procesorius gali programuoti DMA.

Kai DMA yra idealioje būsenoje ir nebegauna jokių papildomų kanalų užklausų, ji perduoda HRQ signalą procesoriui ir persijungia į aktyvią būseną, kurioje gali pradėti duomenų perdavimą per serijos, pavogimo ciklo režimu arba permatomą režimą.

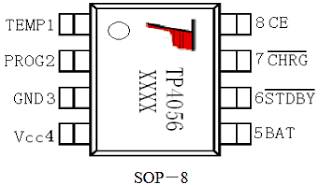

8237 smeigtukų schema

8257 DMA valdiklis

Suporuotas su vienu „Intel 8212“ įvesties / išvesties prievado įrenginiu, 8257 DMA valdiklis sudaro pilną 4 kanalų kanalą DMA valdiklis . Gavęs perdavimo prašymą, 8257 valdiklis-

- Įgauna sistemos magistralės valdymą iš procesoriaus.

- Pripažįstamas periferinis įrenginys, prijungtas prie aukščiausio prioriteto kanalo.

- Mažiausiai reikšmingi atminties adreso bitai perkeliami per sistemos magistralės adresų eilutes A0-A7.

- Reikšmingiausias 8 bitų atminties adreso duomenų linijomis nukreipiami į 8212 įvesties / išvesties prievadą.

- Generuoja atitinkamus valdymo signalus duomenims perduoti tarp išorinių įrenginių ir adresinės atminties vietų.

- Perkėlus nurodytą skaičių baitų, valdiklis informuoja CPU perdavimo pabaigą, įjungdamas terminalų skaičiavimo (TC) išėjimą.

Kiekviename kanale 8257 yra du 16 bitų registrai - 1) DMA adresų registras ir 2) terminalų skaičiaus registras, kuris turėtų būti inicijuotas prieš įjungiant kanalą. Pirmosios atminties vietos, į kurią reikia patekti, adresas įkeliamas į DMA adresų registrą. Apatinės 14 bitų vertės, įkeliamos į terminalų skaičiavimo registrą, skaičius rodo DMA ciklų skaičių atėmus vieną prieš įjungiant terminalų skaičiavimo išvestį. Kanalo operacijos tipas nurodomas dviem reikšmingiausiais terminalų skaičiavimo registro bitais.

8257 kaiščių schema

DMA valdiklio pranašumai ir trūkumai

DMA valdiklio privalumai ir trūkumai apima šiuos dalykus.

Privalumai

- DMA pagreitina atminties operacijas apeinant procesoriaus dalyvavimą.

- Sumažėja procesoriaus darbo perkrova.

- Kiekvienam perdavimui reikalingi tik keli laikrodžio ciklų skaičiai

Trūkumai

- Talpyklos darnos problema gali būti matoma, kai DMA naudojamas duomenims perduoti.

- Padidina sistemos kainą.

DMA ( Tiesioginė prieiga prie atminties ) valdiklis naudojamas grafikos plokštėse, tinklo plokštėse, garso plokštėse ir pan. ... DMA taip pat naudojamas mikroschemų procesoriams perduoti mikroschemoms. Veikdamas vienu iš trijų savo režimų, DMA gali žymiai sumažinti procesoriaus apkrovą. Su kuriuo iš DMA režimų dirbote? Kuris iš jūsų laikomų režimų yra efektyvesnis?