Valdymo blokas yra pagrindinis kompiuteriuose esančio centrinio procesoriaus (CPU) komponentas, kuris gali nukreipti operacijas programos vykdymo metu procesorius /kompiuteris. Pagrindinė valdymo bloko funkcija yra gauti ir vykdyti instrukcijas iš kompiuterio atminties. Jis gauna iš vartotojo įvesties nurodymą / informaciją ir paverčia jį į valdymo signalai , kurios tada atiduodamos procesoriui tolesniam vykdymui. Jis įtrauktas į Johno Neumanno sukurtą Von Neumanno architektūros dalį. Ji yra atsakinga už laiko signalų ir valdymo signalų teikimą ir nurodo procesoriaus vykdomą programą. Šiuolaikiniuose kompiuteriuose jis įtrauktas kaip vidinė procesoriaus dalis. Šiame straipsnyje aprašoma išsami informacija apie valdymo bloką.

Kas yra valdymo blokas?

Komponentas, kuris gauna įvesties signalą / informaciją / instrukciją iš vartotojo ir paverčiamas valdymo signalais vykdymui procesoriuje. Jis valdo ir valdo pagrindinę atmintį, aritmetinį ir loginį vienetą (ALU), įvesties ir išvesties įrenginius, taip pat atsako už instrukcijas, siunčiamas į kompiuterio centrinį procesorių. Jis pateikia instrukcijas iš Pagrindinė ATMINTIS procesoriaus ir siunčiamas į procesoriaus instrukcijų registrą, kuriame yra registro turinys.

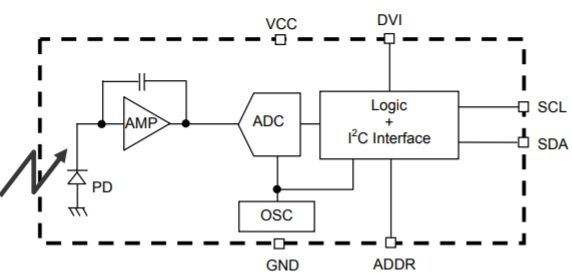

Valdymo bloko blokinė schema

Valdymo blokas konvertuoja įvestį į valdymo signalus, tada siunčiamas procesoriui ir nurodo programos vykdymą. Operacijas, kurias reikia atlikti, procesorius nurodo kompiuteryje. Daugiausia centrinis procesorius (CPU) ir Grafinio apdorojimo blokas (GPU) reikia valdymo bloko kaip vidinės dalies. Valdymo bloko schema parodyta aukščiau.

Valdymo bloko komponentai

Šio įrenginio komponentai yra instrukcija registrai , valdymo signalai procesoriuje, valdymo signalai į / iš magistralės, valdymo magistralė, įvesties vėliavos ir laikrodžio signalai.

Laidinio valdymo bloko komponentai yra instrukcijų registras (jame yra kodo ir adreso laukas), laiko vienetas, valdymo būsena generatorius , valdymo signalo generavimo matrica ir instrukcijų dekoderis.

„Micro“ užprogramuoto valdymo bloko komponentai yra kitas adresų generatorius, valdymo adresų registras, valdymo atmintis ir valdymo duomenų registras.

Funkcijos

The valdymo bloko funkcijos įtraukti šiuos dalykus.

- Jis nukreipia duomenų seką tarp procesoriaus ir kitų įrenginių.

- Jis gali interpretuoti instrukcijas ir valdyti duomenų srautą procesoriuje.

- Jis generuoja valdymo signalų seką iš gautų komandų ar komandų iš komandų registro.

- Ji yra atsakinga už tokių vykdymo vienetų kaip ALU, duomenų buferių ir registrų valdymą kompiuterio procesoriuje.

- Jis turi galimybę gauti, iššifruoti, tvarkyti vykdymą ir saugoti rezultatus.

- Jis negali apdoroti ir saugoti duomenų

- Norėdami perduoti duomenis, jis bendrauja su įvesties ir išvesties įrenginiais ir valdo visus kompiuterio vienetus.

Valdymo bloko dizainas

Tai galima sukurti naudojant du valdymo bloko tipai kurie apima šiuos dalykus.

- Hardwire pagrindu

- Mikroprogramuotas (vieno lygio ir dviejų lygių)

Laidinis valdymo blokas

Pagrindinis laidinio valdymo bloko dizainas parodytas aukščiau. Šio tipo valdymo signalus generuoja speciali aparatinė įranga loginė grandinė be jokių grandinės struktūros pokyčių. Tokiu būdu sugeneruoto signalo negalima modifikuoti vykdant procesoriuje.

Pagrindiniai opkodo duomenys (komandos operacijos kodas išsiunčiamas dekodavimui į komandų dekoderį. Nurodymas dekoderis yra dekoderių rinkinys, skirtas iššifruoti įvairių tipų duomenis opcode. Dėl to gaunami išėjimo signalai, kuriuose yra aktyviųjų signalų vertės, kurios pateikiamos kaip įvestis į matricos generatorių, kad generuotų valdymo signalus, kuriuos kompiuterio procesorius vykdo programai.

„Hardwire“ pagrindu valdomas valdymo blokas

Matricos generatorius pateikia valdymo bloko būsenas ir signalus iš procesoriaus (pertraukimo signalus). Matrica yra sukurta kaip programuojamas logikos masyvas . Matricos generatoriaus sugeneruoti valdymo signalai pateikiami kaip įvestis į kitą generatoriaus matricą ir derinami su laiko vieneto, kuriame yra stačiakampio formos, laiko signalais.

Norėdami gauti naują komandą, valdymo blokas virsta pradiniu naujos komandos vykdymo etapu. Valdymo blokas lieka pradiniame arba pirmame etape tol, kol nepakinta kompiuterio laiko signalai, įvesties signalai ir instrukcijos būsenos. Valdymo bloko būsenos pokytį galima padidinti, jei pasikeičia kuris nors iš sugeneruotų signalų.

Kai įvyksta išorinis signalas arba nutrūksta, valdymo blokas pereina į kitą būseną ir atlieka pertraukimo signalo apdorojimą. Vėliavos ir būsenos yra naudojamos norimoms būsenoms pasirinkti, kad būtų įvykdytas instrukcijos vykdymo ciklas.

Paskutinėje būsenoje valdymo blokas gauna kitą komandą ir išsiunčia išvestį į programos skaitiklį, tada į atminties adresų registrą, į buferio registrą ir po to į komandų registrą, kad galėtų perskaityti instrukciją. Galiausiai, jei paskutinė instrukcija (kurią pateikia valdymo blokas) yra pabaigos instrukcija, ji pereina į procesoriaus veikimo būseną ir laukia, kol vartotojas nurodys kitą programą.

Mikroprogramuotas valdymo blokas

Šio tipo valdymo saugykla naudojama valdymo signalams, užkoduotiems vykdant programą, saugoti. Valdymo signalas nėra sugeneruojamas iškart ir dekoduojamas, nes mikroprograma saugo adresų lauką valdymo parduotuvėje. Visas procesas yra vienas lygis.

Mikrooperacijos atliekamos vykdant mikro instrukcijas programoje. „Micro“ programuoto valdymo bloko schema parodyta aukščiau. Iš schemos mikrokomandos adresas gaunamas iš valdymo atminties adresų registro. Visa valdymo bloko informacija yra nuolat saugoma valdymo atmintyje, vadinamoje ROM.

Mikroprogramuotas valdymo blokas

Mikro instrukcijas iš valdymo atminties laiko valdymo registras. Kadangi mikro instrukcija yra kontrolinio žodžio pavidalu (jame yra dvejetainės valdymo vertės), kuriam reikalinga 1 ar daugiau mikrooperacijų, kad būtų galima apdoroti duomenis.

Vykdant mikrokomandas, kitas adresų generatorius apskaičiavo kitą mikrokomandos adresą ir tada išsiuntė į valdymo adresų registrą skaityti kitos mikrokomandos.

Mikroprogramos mikrooperacijų seką atlieka kitas adresų generatorius ir veikia kaip mikroprogramų sekvenceris, kad gautų sekos adresą, t. Y., Perskaitytą iš valdymo atminties.

Valdymo bloko „Verilog“ kodas

Valdymo bloko „Verilog“ kodas parodytas žemiau.

`įtraukti„ prj_definition.v “

modulis „CONTROL_UNIT“ (MEM_DATA, RF_DATA_W, RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2, RF_READ, RF_WRITE, ALU_OP1, ALU_OP2, ALU_OPRN, MEM_ADDR, MEM_READ, MEM_WRITE, RF_DATA_R1, RF_DATA_1

// Išvesties signalai

// Registro failo išvestys

išvestis [`DATA_INDEX_LIMIT: 0] RF_DATA_W

išvestis [`ADDRESS_INDEX_LIMIT: 0] RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

išvestis RF_READ, RF_WRITE

// ALU išėjimai

išvestis [`DATA_INDEX_LIMIT: 0] ALU_OP1, ALU_OP2

išvestis [`ALU_OPRN_INDEX_LIMIT: 0] ALU_OPRN

// Atminties išvestys

išvestis [`ADDRESS_INDEX_LIMIT: 0] MEM_ADDR

išvestis MEM_READ, MEM_WRITE

// Įvesties signalai

įvestis [`DATA_INDEX_LIMIT: 0] RF_DATA_R1, RF_DATA_R2, ALU_RESULT

įvestis ZERO, CLK, RST

// Inout signalas

inout [`DATA_INDEX_LIMIT: 0] MEM_DATA

// Valstybiniai tinklai

laidas [2: 0] proc_state

// turi programos skaitiklio vertę, saugo dabartinę instrukciją, „stack pointer“ registrą

reg MEM_READ, MEM_WRITE

reg. MEM_ADDR

reg ALU_OP1, ALU_OP2

reg ALU_OPRN

reg. RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

reg RF_DATA_W

reg [1: 0] būsena, kita stotis

PROC_SM būsenos mašina (.STATE (proc_state), CLK (CLK), RST (RST))

visada @ (pozedge CLK)

pradėti

jei (RST)

valstija<= RST

Kitas

valstija<= next_state

galas

visada @ (valstija)

pradėti

MEM_READ = 1’b0 MEM_WRITE = 1’b0 MEM_ADDR = 1’b0

ALU_OP1 = 1’b0 ALU_OP2 = 1’b0 ALU_OPRN = 1’b0

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0 RF_ADDR_W = 1’b0 RF_DATA_W = 1’b0

byla (valstija)

„PROC_FETCH: pradėk

next_state = 'PROC_DECODE

MEM_READ = 1’b1

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0

RF_ADDR_W = 1’b1

galas

„PROC_DECODE: pradėti

next_state = 'PROC_EXE

MEM_ADDR = 1’b1

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

MEM_WRITE = 1’b1

RF_ADDR_R1 = 1’b1 RF_ADDR_R2 = 1’b1

galas

„PROC_EXE: pradėti

next_state = 'PROC_MEM

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

RF_ADDR_R1 = 1’b0

galas

„PROC_MEM: pradėti

next_state = 'PROC_WB

MEM_READ = 1’b1 MEM_WRITE = 1’b0

galas

„PROC_WB: pradėk

next_state = 'PROC_FETCH

MEM_READ = 1’b1 MEM_WRITE = 1’b0

galas

galinė dalis

galas

endmodulis

modulis PROC_SM (VALSTYBĖ, CLK, RST)

// įvesties sąrašas

įvestis CLK, RST

// rezultatų sąrašas

išvestis [2: 0] VALSTYBĖ

// įvesties sąrašas

įvestis CLK, RST

// išvesties sąrašas

išėjimas STATE

reg [2: 0] VALSTYBĖ

reg [1: 0] būsena

reg [1: 0] kita stotis

reg PC_REG, INST_REG, SP_REF

`apibrėžti PROC_FETCH 3'h0

`apibrėžti PROC_DECODE 3'h1

`apibrėžti PROC_EXE 3'h2

`apibrėžti PROC_MEM 3'h3

`apibrėžti PROC_WB 3'h4

// būsenos iniciacija

pradinis

pradėti

būsena = 2’bxx

next_state = 'PROC_FETCH

galas

// iš naujo nustatyti signalo tvarkymą

visada @ (posedge RST)

pradėti

būsena = 'PROC_FETCH

next_state = 'PROC_FETCH

galas

visada @ (pozedge CLK)

pradėti

būsena = kita stotis

galas

visada @ (valstija)

pradėti

jei (nurodykite === `PROC_FETCH)

pradėti

next_state = 'PROC_DECODE

spausdinimo instrukcija (INST_REG)

galas

jei (nurodykite === `PROC_DECODE)

pradėti

next_state = 'PROC_EXE

galas

jei (nurodykite === `PROC_EXE)

pradėti

next_state = 'PROC_MEM

spausdinimo instrukcija (SP_REF)

galas

jei (būsena === `PROC_MEM)

pradėti

next_state = 'PROC_WB

galas

jei (būsena === 'PROC_WB)

pradėti

next_state = 'PROC_FETCH

spausdinimo instrukcija (PC_REG)

galas

galas

užduoties spausdinimo_ instrukcija

įvesti [`DATA_INDEX_LIMIT: 0] inst

reg [5: 0] opcode

reg [4: 0] rs

reg [4: 0] rt

reg [4: 0] p

reg [4: 0] shamt reg [5: 0] funct reg [15: 0] tiesioginis reg [25: 0] adresas

pradėti

// analizuoti instrukciją

// R tipo

{opcode, rs, rt, rd, shamt, funct} = inst

// Aš-tipas

{opcode, rs, rt, momentinis} = inst

// J tipo

{opcode, address} = inst

$ write („@% 6dns -> [0X% 08h]“, $ time, inst)

didžiosios ir mažosios raidės (opcode) // R-Type

6'h00: pradžia

atvejis (funkcija)

6’h20: $ write („pridėti r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h22: $ write („sub r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h2c: $ write („mul r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h24: $ write („ir r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h25: $ write („arba r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h27: $ write („nei r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h2a: $ write („slt r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h00: $ write („sll r [% 02d],% 2d, r [% 02d]“, rs, shamt, rd)

6’h02: $ write („srl r [% 02d], 0X% 02h, r [% 02d]“, rs, shamt, rd)

6’h08: $ write („jr r [% 02d]“, rs)

numatytasis: $ write (“”)

galinė dalis

galas

// Aš-tipas

6’h08: $ write („addi r [% 02d], r [% 02d], 0X% 04h“, rs, rt, nedelsiant)

6’h1d: $ write („muli r [% 02d], r [% 02d], 0X% 04h“, rs, rt, nedelsiant)

6’h0c: $ write („andi r [% 02d], r [% 02d], 0X% 04h“, rs, rt, nedelsiant)

6’h0d: $ write („ori r [% 02d], r [% 02d], 0X% 04h“, rs, rt, nedelsiant)

6’h0f: $ write („lui r [% 02d], 0X% 04h“, rt, nedelsiant)

6’h0a: $ write („slti r [% 02d], r [% 02d], 0X% 04h“, rs, rt, nedelsiant)

6’h04: $ write („beq r [% 02d], r [% 02d], 0X% 04h“, rs, rt, nedelsiant)

6’h05: $ write („bne r [% 02d], r [% 02d], 0X% 04h“, rs, rt, nedelsiant)

6’h23: $ write („lw r [% 02d], r [% 02d], 0X% 04h“, rs, rt, nedelsiant)

6’h2b: $ write („sw r [% 02d], r [% 02d], 0X% 04h“, rs, rt, nedelsiant)

// J-tipas

6’h02: $ write („jmp 0X% 07h“, adresas)

6’h03: $ write („jal 0X% 07h“, adresas)

6’h1b: $ write („push“)

6’h1c: $ write („pop“)

numatytasis: $ write (“”)

galinė dalis

$ write („ n“)

galas

pabaigos užduotis

pabaigos modulis

DUK

1). Koks yra valdymo bloko darbas?

Valdymo bloko darbas yra nukreipti duomenų srautą ar instrukcijas, kurias kompiuterio procesorius vykdo. Jis valdo, valdo ir koordinuoja pagrindinę atmintį, ALU, registrus, įvesties ir išvesties vienetus. Jis gauna instrukcijas ir generuoja vykdymo valdymo signalus.

2). Kas yra kontrolinė atmintis?

Valdymo atmintis paprastai yra RAM arba ROM, skirta saugoti valdymo registro adresą ir duomenis.

3). Kas yra „Wilkes“ valdymo blokas?

Nuoseklus ir kombinacinės grandinės laidinio valdymo bloko pakeičiamas Wilkes valdymo bloku. Jis naudoja atminties įrenginį mikroprogramos instrukcijų sekoms saugoti.

4). Kas yra laidinis valdymo blokas?

Laidinis valdymo blokas generuoja valdymo signalus, keisdamasis iš vienos būsenos į kitą būseną kiekviename laikrodžio pulse be fizinių grandinės pokyčių. Valdymo signalų generavimas priklauso nuo instrukcijų registro, dekoderio ir pertraukimo signalų.

5). Kas yra kontrolinė atmintis?

Valdymo bloko informacija arba duomenys laikinai arba visam laikui saugomi valdymo atmintyje.

Valdymo atmintis yra dviejų tipų. Tai yra laisvosios kreipties atmintis (RAM) ir tik skaitoma atmintis (ROM).

Taigi visa tai yra apibrėžimas, komponentai, dizainas, schema, funkcijos ir valdymo bloko tipai . Štai jums klausimas „Koks yra kontrolinių adresų registro tikslas?“