The fazėje užrakinta kilpa yra vienas pagrindinių blokų šiuolaikinėse elektroninėse sistemose. Paprastai jis naudojamas daugialypėje terpėje, komunikacijoje ir daugelyje kitų programų. Yra du skirtingi PLL tipai - linijiniai ir netiesiniai. Netiesinį yra sunku ir sudėtinga projektuoti realiame pasaulyje, tačiau tiesinio valdymo teorija yra gerai modeliuojama analoginėse PLL. PLL įrodė, kad daugumai elektroninių programų pakanka linijinio modelio.

Kas yra fazėje užrakinta kilpa?

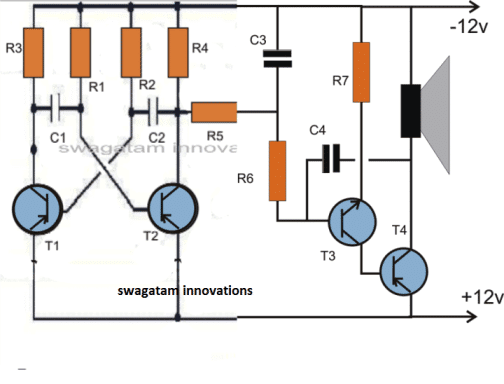

Fazėje užrakinta kilpa susideda iš fazės detektoriaus ir įtampa valdomo osciliatoriaus. Fazės detektoriaus išėjimas yra įtampa valdomo osciliatoriaus (VCO) įėjimas, o VCO išėjimas yra prijungtas prie vieno iš fazės detektoriaus įėjimų, kuris parodytas žemiau pagrindinėje bloko schemoje. Kai šie du prietaisai yra tiekiami vienas kitam, kilpa susidaro.

PAGRINDINĖ FASĖS UŽRAKINTO LIPTO DIAGRAMA

Blokinė schema ir PLL veikimo principas

Fazėje užrakinta kilpa susideda iš fazės detektoriaus, a įtampos valdomas osciliatorius ir tarp jų yra fiksuotas žemo dažnio filtras. Įvesties signalą „Vi“ su įėjimo dažniu „Fi“ pripažįsta fazės detektorius. Iš esmės fazių detektorius yra palyginamasis kad palyginamas įvesties dažnis fi per grįžtamojo ryšio dažnį fo. Fazės detektoriaus išvestis yra (fi + fo), kuri yra nuolatinė įtampa. Iš fazės detektoriaus, t. Y. Nuolatinės srovės įtampa įvedama į žemo dažnio filtrą (LPF), jis pašalina aukšto dažnio triukšmą ir sukuria pastovų nuolatinės srovės lygį, t. Y. Fi-Fo. Vf taip pat yra dinaminė PLL charakteristika.

PLL blokinė schema

Žemo dažnio filtro išėjimas, ty nuolatinės srovės lygis, perduodamas VCO. Įvesties signalas yra tiesiogiai proporcingas VCO (fo) išėjimo dažniui. Įvesties ir išvesties dažniai lyginami ir koreguojami per grįžtamąjį ryšį, kol išėjimo dažnis bus lygus įėjimo dažniui. Taigi, PLL veikia kaip laisvas bėgimas, fiksavimas ir fazių užraktas.

Kai nėra įvestos įėjimo įtampos, sakoma, kad tai laisvai einantis etapas. Kai tik LOJ taikomas įėjimo dažnis pasikeičia ir sukuria išėjimo dažnį palyginimui, jis vadinamas fiksavimo stadija. Žemiau pateiktame paveiksle parodyta blokinė PLL schema.

Fazės užrakto kilpos detektorius

Fazės užrakto kontūro detektorius palygina VCO įėjimo dažnį ir išėjimo dažnį, kad gautų nuolatinę įtampą, kuri yra tiesiogiai proporcinga dviejų dažnių fazių skirtumui. Analoginis ir skaitmeninis signalai naudojami fazėje užrakintoje grandinėje. Dauguma monolitinio PLL integruoti grandynai naudokite analoginį fazės detektorių, o dauguma fazių detektorių yra skaitmeninio tipo. Dvigubo subalansuoto mišinio grandinė paprastai naudojama analoginiuose fazių detektoriuose. Kai kurie įprasti fazių detektoriai pateikti žemiau:

Išskirtinis ARBA fazių detektorius

Išskirtinis ARBA fazių detektorius yra CMOS IC 4070 tipo. Įvesties ir išėjimo dažniai pritaikomi fazės detektoriui EX OR. Norint gauti aukštą išvestį, bent vienas įvestis turėtų būti mažas, o kitos išvesties sąlygos yra žemos, kas parodyta žemiau esančioje tiesos lentelėje. Panagrinėkime bangos formą, įvesties ir išėjimo dažnius, ty fi ir fo fazių skirtumas yra 0 laipsnių. Tada lyginamojo aparato nuolatinė išėjimo įtampa bus fazių skirtumo tarp dviejų įėjimų funkcija.

| būti | fo | Vdc |

žemas | žemas | žemas |

žemas | aukštas | aukštas |

aukštas | Žemas | aukštas |

Aukštas | Aukštas | žemas |

Fazių skirtumo tarp fi ir fo funkcijos yra tokios, kaip parodyta nuolatinės srovės išėjimo įtampos diagramoje. Jei fazės detektorius yra 180 laipsnių, išėjimo įtampa yra didžiausia. Jei tiek įėjimo, tiek išėjimo dažniai yra kvadratinės bangos, naudojami šie fazių detektoriai.

Išskirtinis ARBA fazių detektorius

Krašto paleidimo fazės detektorius

Krašto paleidimo fazės detektorius naudojamas, kai įėjimo ir išėjimo dažniai yra impulsinės bangos formos, o tai yra mažiau nei 50% darbo ciklo. R-S flip flop naudojamas fazių detektoriams, kurie parodyti žemiau esančiame paveikslėlyje. Į iš R-S šlepetė , du NOR vartai yra susieti tarpusavyje. Fazės detektoriaus išvestis gali pakeisti savo loginę būseną suaktyvindama R-S flip flop. Teigiamas įėjimo ir išėjimo dažnių kraštas gali pakeisti fazės detektoriaus išėjimą.

Krašto paleidimo fazės detektorius

Monolitinis fazių detektorius

Monolitinis fazių detektorius yra CMOS tipo, t. Y. IC 4044. Jis yra labai kompensuojamas dėl harmoninio jautrumo ir darbo ciklo problemų atsisakoma, nes grandinė gali reaguoti tik į įėjimo signalo perėjimą. Kritinėse programose tai yra labiausiai karščiuojantis fazių detektorius. Nepriklausomi amplitudės pokyčiai neturi fazės paklaidos, išėjimo paklaidos įtampos ir įvesties bangos formos darbo ciklo.

Fazės užrakinto ciklo programos

- FM demoduliavimo tinklai FM operacijoms

- Jis naudojamas variklio greičio valdikliai ir stebėjimo filtrai.

- Jis naudojamas demoduliuojančių nešėjų dažnių dekodavimo dažniuose.

- Jis laiku naudojamas skaitmeniniams keitikliams.

- Jis naudojamas Jitter mažinimui, iškreipimo slopinimui, laikrodžio atstatymui.

Tai viskas apie fazės užrakto ciklo veikimo ir veikimo principą ir jo taikymą. Tikimės, kad straipsnyje pateikta informacija yra naudinga jums norint ką nors sužinoti apie projektą ir jį suprasti. Be to, jei turite klausimų apie šį straipsnį ir toliau elektriniai ir elektroniniai projektai galite pakomentuoti žemiau esančiame skyriuje. Štai jums klausimas, kaip geriausia modeliuoti stabilumo PLL?

Nuotraukų kreditai:

- Blokinė PLL schema šiandien

- Išskirtinis ARBA fazių detektorius sanfoundry

- Krašto paleidimo fazės detektorius MOKYMOSI-ELEKTRONIKA