Kasdieniame gyvenime mes dažnai bendraujame su kitais, naudodami kelis jų tipus ryšių sistemos . Ši ryšio sistema gali būti skirstoma į įvairius tipus, pavyzdžiui, radijo ryšio sistemą, telekomunikacijų sistemą, Belaidžio ryšio sistema , Optinio ryšio sistema ir pan. Kad visos šios ryšio sistemos veiktų efektyviai, mums reikia kelių valdymo sistemų, tokių kaip fazės užrakinta kilpa, kooperatyvus valdymas, valdymas tinkle ir pan.

Kas yra faze užrakinta kilpa (PLL)?

Faze užrakinta kilpa naudojama kaip valdymo sistema skirtingoms operacijoms valdyti daugelyje ryšių sistemų, kompiuterių ir daugelyje elektroninės programos . Jis naudojamas generuoti išėjimo signalą, kurio fazė susijusi su įvesties signalo faze.

Yra įvairių tipų PLL, tokių kaip Analoginis arba Linijinis PLL, Skaitmeninis PLL, Programinės įrangos PLL, Neuronal PLL ir visi skaitmeniniai PLL.

Fazės užrakinto ciklo operacija

Ryšio sistemose PLL operaciją galima paaiškinti apsvarstžius analoginės ir skaitmeninės sistemos .

Analoginis fazių užrakintas ryšių sistemų ciklas

Iš esmės PLL yra servo kilpos forma, o pagrindinį PLL sudaro trys pagrindiniai elementai: fazių palyginimas / detektorius, kilpos filtras ir įtampos valdomas osciliatorius .

Fazė užrakinta kilpa

Pagrindinė PPL operacijos koncepcija yra dviejų signalų fazių palyginimas (paprastai lyginamos įvesties ir išvesties signalo fazės). Taigi fazių skirtumas tarp įėjimo ir išėjimo signalo gali būti naudojamas valdant kilpos dažnį. Nors matematinė analizė yra labai sudėtinga, tačiau PLL operacija yra labai paprasta.

Daugelyje ryšių sistemų PLL naudojamas įvairiems tikslams:

- Fazės ar dažnio moduliacija , jis naudojamas kaip Demoduliatorius.

- Norėdami stebėti arba sinchronizuoti du skirtingo dažnio signalus.

- Norėdami pašalinti didelius triukšmus nuo mažų signalų.

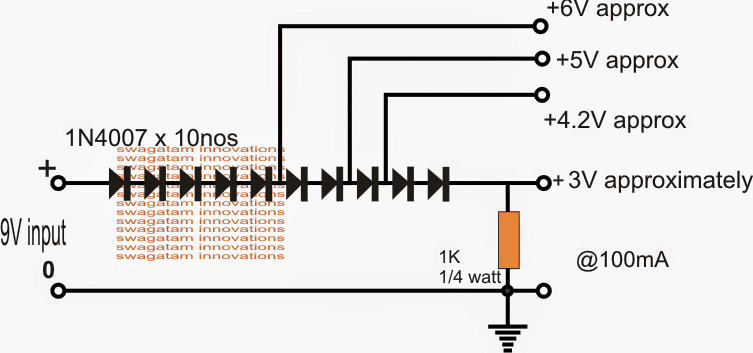

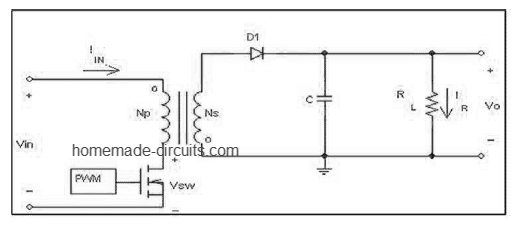

Žemiau pateiktame paveikslėlyje parodytas pagrindinis PLL, kurį sudaro fazės detektorius, įtampos valdomas osciliatorius (VCO), kilpos filtras.

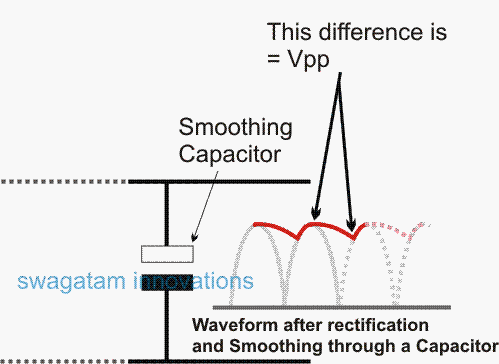

PLL įtampos valdomas osciliatorius sukuria signalą ir šis VCO signalas perduodamas fazės detektoriui. Fazės detektorius palygina šį signalą su etaloniniu signalu ir taip sukuria klaidos įtampą arba įtampos skirtumą. Šis fazės detektoriaus klaidos signalas tiekiamas į žemo dažnio filtrą, kad būtų pašalinti aukšto dažnio signalo elementai, jei jie yra, ir valdytų daugelį kilpos savybių. Tada kilpos filtro išvestis tiekiama tiekiant įtampos valdomo osciliatoriaus valdymo terminalo derinimo įtampą.

Juntamas šios derinimo įtampos pokytis, kad sumažėtų fazių skirtumas tarp dviejų signalų (įvesties ir išvesties), taigi ir dažnis tarp jų. Iš pradžių PLL neužsiblokuoja ir klaidos įtampa tempia VCO dažnį link atskaitos, kol paklaida negali būti toliau sumažinta, o tada kilpa užsiblokuoja.

Tikroji dviejų signalų (įvesties ir išvesties) paklaida sumažinama iki labai mažo lygio naudojant stiprintuvą tarp įtampos valdomo osciliatoriaus ir fazės detektoriaus. Jei PLL yra užrakinta, bus sukurta pastovios būsenos klaidos įtampa. Ši pastoviosios būsenos paklaidos įtampa rodo, kad tarp etaloninio signalo ir VCO fazių skirtumo nėra. Taigi galime sakyti, kad dviejų signalų (įvesties ir išvesties signalų) dažnis yra visiškai vienodas.

Skaitmeninis fazės užrakintas ryšių sistemų ciklas

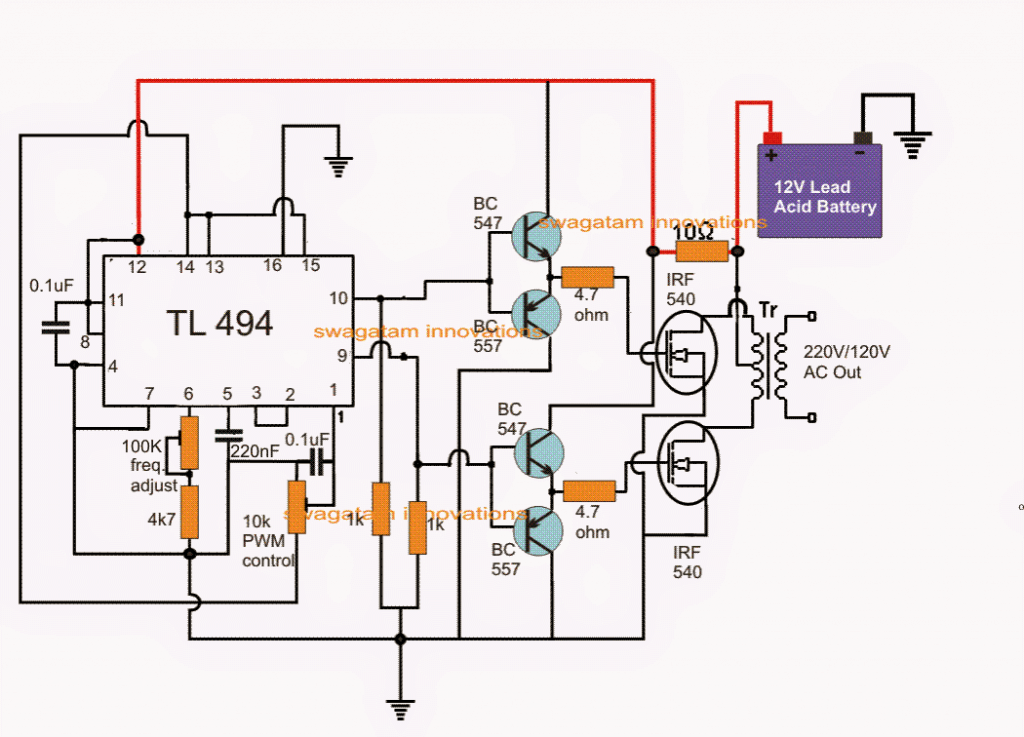

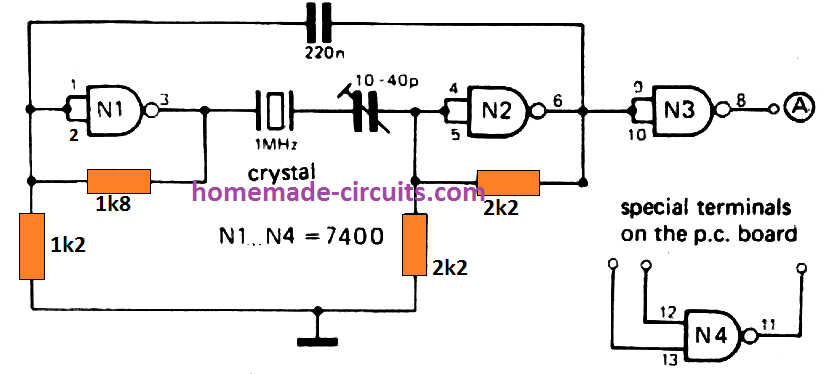

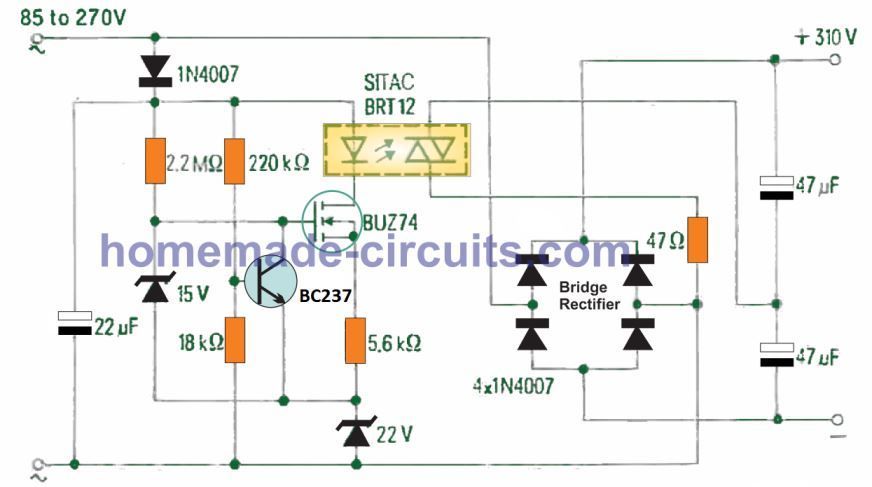

Paprastai analoginius PLL sudaro analoginio fazės detektorius, įtampa valdomas osciliatorius ir žemo dažnio filtras. Panašiai skaitmeninę fazę užrakinta kilpa susideda iš skaitmeninės fazės detektoriaus, a serijinis pamainos registras , stabilus - vietinis laikrodžio signalas.

Skaitmeninė fazė užrakinta kilpa

Skaitmeninės įvesties pavyzdžiai išgaunami iš priimto signalo ir šiuos mėginius gauna nuoseklusis poslinkio registras, kurį valdo laikrodžio impulsai, tiekiami iš vietinio-laikrodžio signalo. Fazės korektoriaus grandinė, reikalaujanti vietinio laikrodžio, naudojama stabilaus laikrodžio signalo atkūrimui fazėje su priimtu signalu lėtai reguliuojant fazę, kad atitiktų gauto signalo fazę.

Šį koregavimą galima atlikti remiantis kiekvieno bitų didelės spartos pavyzdžiu, naudojant korekcijos logiką. Gautas signalo pavyzdys, gautas imant gautą signalą vietiniu laikrodžio greičiu, dedamas į pamainų registrą.

Reikiamą fazės reguliavimą galima nustatyti stebint priimto signalo pavyzdžių rinkinį. Sakoma, kad du laikrodžiai yra fazėje tada ir tik tuo atveju, jei gaunamo bito centras yra pamainų registro centre. Fazių reguliatorius skirtas kompensuoti, jei regeneruotas laikrodis atsilieka arba veda atskaitos signalą.

Fazės užrakinto ciklo taikymas

- PLL dažnai naudojami sinchronizavimo tikslais ir bitų sinchronizavimui, simbolių sinchronizavimui, nuosekliai demoduliacijai ir slenksčio išplėtimui kosminėje komunikacijoje.

- Dažnio moduliuojamus signalus galima demoduliuoti naudojant PLL.

- Naujas dažnis, kuris yra atskaitos dažnio kartotinis radijo ryšio siųstuvai ir sintetinamas išlaikant etaloninio dažnio stabilumą nauju dažniu, galima pasiekti PLL.

- Yra daugybė programų, skirtų PLL, daugelyje ryšių sistemų, kompiuterių ir daugelyje elektroninės grandinės .

- Žemiau pateiktoje PLL programoje aprašomas PLL naudojimas kaip įtampa dažnio keitiklis .

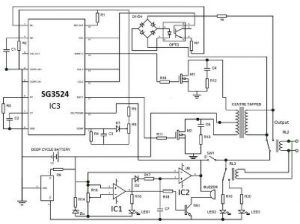

Įtampa į dažnio keitiklį (VFC) naudojant PLL

Ryšio sistemose reikalaujama siųsti signalus (čia apsvarstykite analoginį signalą) su dideliu atstumu visiškai tiksliai. Šiuo tikslu naudojamas įtampos ir dažnio keitiklis, nes naudojant optinius izoliatorius, koaksialines ar vytos poros linijas, radijo ryšius lengva siųsti dažnio signalą, nesukeliant jokių trukdžių dideliu atstumu. optinio pluošto jungtys .

Yra dviejų tipų įtampos ir dažnio keitikliai, būtent multivibratoriaus tipas VFC ir įkrovos balanso tipas.

Multivibratoriaus tipas VFC

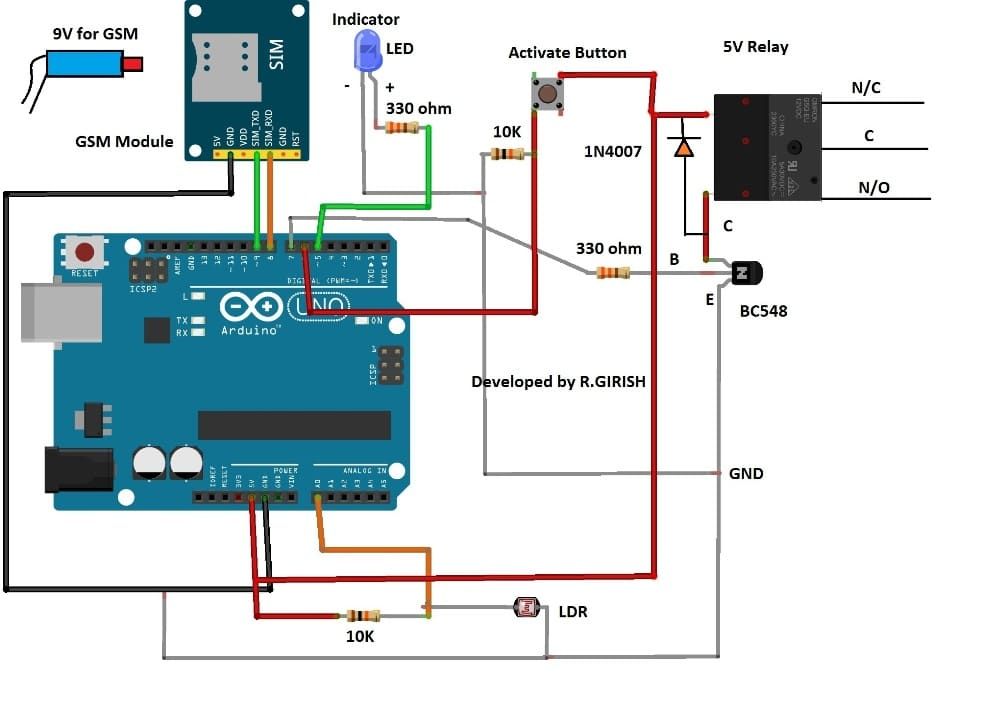

Multivibratorius VFC

VFC tipo multivibratoriuje kondensatorius įkraunamas ir iškraunamas naudojant srovę, gautą iš įėjimo įtampos. Stabili atskaitos įvestis suteikiama nustatyti perjungimo slenksčius, o išėjimo dažnis yra proporcingas įėjimo įtampai ir turi vienybės ženklo ir erdvės santykį.

Įkrovos balanso tipas VFC

Įkrovos balansas VFC

Įkrovos balansą VFC sudaro integratorius, lygintuvas ir tikslaus įkrovimo šaltinis. Kai integratoriui įvedama įvestis, jis įkraunamas ir, jei šio integratoriaus išvestis pasiekia lyginamąjį slenkstį, įsijungia įkrovimo šaltinis ir fiksuotas mokestis pašalinamas iš integratoriaus. Pašalinto įkrovimo greitis turi būti lygus tiekiamo įkrovos greičiui, kad įkrovos šaltinio sukeltas dažnis ir įvestis į integratorių būtų proporcingi vienas kitam.

Taigi šiame straipsnyje trumpai aprašoma fazės užrakto ciklo sistema ryšių sistemoje. Be to, šis straipsnis gali būti techniškai išplėstas, atsižvelgiant į jūsų pasiūlymus ir klausimus. Taigi galite kreiptis į mus dėl bet kokios techninės pagalbos, paskelbdami savo komentarus žemiau.