Šiame įraše sužinosime, kaip sukurti NOT, AND, NAND, OR ir NOR loginius vartus naudojant atskirus tranzistorius. Pagrindinis tranzistorių loginių vartų naudojimo pranašumas yra tas, kad jie gali veikti net esant 1,5 V įtampai.

Kai kuriose elektroninėse programose turimos įtampos gali nepakakti TTL ar net CMOS IC maitinimui. Tai ypač pasakytina apie įtaisus, kurie veikia su baterijomis. Be abejo, jūs visada turite 3 voltų loginio IC parinktį. Tačiau jie ne visada yra lengvai prieinami entuziastui ar eksperimentuotojui, ir jie neveikia žemiau nustatytų įtampos specifikacijų (paprastai mažesnė nei 2,5 volto nuolatinė srovė).

Be to, baterijomis maitinamoje programoje gali būti vietos tik vienai 1,5 volto baterijai. Na, ką tada darysi? Paprastai IC loginiai vartai galėtų būti pakeistas tranzistoriniais loginiais vartais. Kiekvienam konkrečiam loginiam vartui paprastai reikia tik kelių tranzistorių, o tipinei NOT vartų keitiklio logikai reikalingas tik vienas tranzistorius.

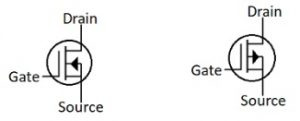

FET ir bipolinis tranzistorius

Lauko efekto tranzistoriai (FET) vs bipoliniai tranzistoriai : kuris yra geresnis žemos įtampos loginių grandinių pasirinkimas? Viena puiki savybė FAKTAI yra tai, kad jų „įjungimo“ pasipriešinimas yra neįtikėtinai mažas. Be to, jiems reikia labai mažos vartų įjungimo srovės.

Tačiau jie turi vieną apribojimą ypač žemos įtampos įrenginiuose. Paprastai vartų įtampos riba yra maždaug vienas voltas. Be to, turima įtampa gali nukristi žemiau optimalaus FET veikimo diapazono, jei prie užtvarų yra prijungtas srovę ribojantis arba nuleidžiamas rezistorius.

Ir atvirkščiai, dvipoliai perjungiami tranzistoriai turi pranašumą naudojant ypač žemos įtampos, vienos baterijos įrenginius, nes jiems įjungti reikia tik 0,6–0,7 volto.

Be to, dauguma įprastų FET, kurie paprastai parduodami burbulinėse pakuotėse artimiausioje elektronikos parduotuvėje, dažnai yra brangesni nei bipoliniai tranzistoriai. Be to, masinį bipolinių tranzistorių paketą paprastai galima įsigyti už poros FET kainą.

FET valdymas reikalauja daug daugiau atsargumo nei bipolinis tranzistorius. Dėl elektrostatinio ir bendro eksperimentinio netinkamo naudojimo FET ypač pažeidžiami. Sudegę komponentai gali sugadinti malonų, kūrybingą eksperimentavimo ar naujovių vakarą, nepamiršti ir emocinio derinimo skausmo.

Tranzistorių perjungimo pagrindai

Šiame straipsnyje paaiškintuose loginės grandinės pavyzdžiuose naudojami bipoliniai NPN tranzistoriai, nes jie yra prieinami ir jiems nereikia specialaus tvarkymo. Kad nesugadintumėte įrenginio arba jį laikančių dalių, prieš prijungdami grandinę reikia imtis tinkamų saugos priemonių.

Nors mūsų grandinės daugiausia sutelktos į dvipolius jungties tranzistorius (BJT), jos taip pat galėjo būti sukonstruotos naudojant FET technologiją.

Pagrindinė jungiklio grandinė yra paprastas tranzistorius, kuris yra vienas iš paprasčiausių konstrukcijų.

NE vartų su vienu tranzistoriumi gamyba

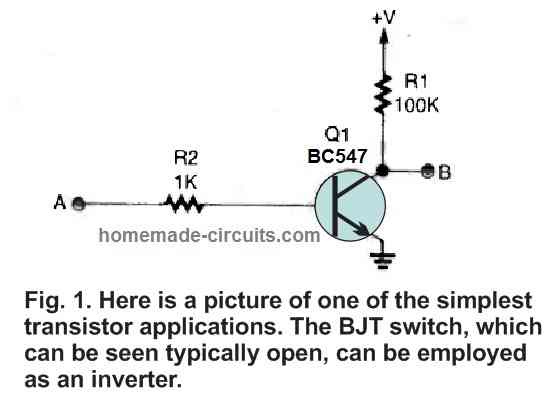

Tranzistoriaus jungiklio schema parodyta 1 paveiksle. Priklausomai nuo to, kaip jis įdiegtas konkrečioje programoje, jungiklis gali būti laikomas žemai arba normaliai atidarytas.

Paprastas NOT vartų keitiklio loginis užtvaras gali būti sukurtas naudojant paprastą perjungimo grandinę, parodytą 1 pav. (kur taškas A yra įvestis). NOT užtvaras veikia taip, kad jei tranzistoriaus bazei (taškas A; Q1) nepateikiamas nuolatinės srovės poslinkis, jis liks išjungtas, todėl išėjime bus aukštas arba loginis 1 (lygus V+ lygiui). punktas B).

Tačiau tranzistorius suaktyvinamas, kai Q1 pagrindui suteikiamas tinkamas poslinkis, o grandinės išėjimas sumažinamas arba iki loginio 0 (beveik lygus nuliniam potencialui). Tranzistorius, žymimas Q1, yra bendrosios paskirties bipolinis tranzistorius arba BC547, kuris paprastai naudojamas mažos galios perjungimui ir stiprintuvams.

Tiktų bet koks jam lygiavertis tranzistorius (pvz., 2N2222, 2N4401 ir kt.). R1 ir R2 reikšmės buvo parinktos taip, kad būtų pasiektas kompromisas tarp mažos srovės nutekėjimo ir suderinamumo. Visose konstrukcijose rezistoriai yra 1/4 vato, 5% vienetų.

Maitinimo įtampa reguliuojama nuo 1,4 iki 6 voltų nuolatinės srovės. Atkreipkite dėmesį, kad grandinė gali veikti kaip buferis, kai apkrovos rezistorius ir išvesties jungtis perkeliami į tranzistoriaus emiterį.

Buferinių vartų sukūrimas naudojant vieną BC547 BJT

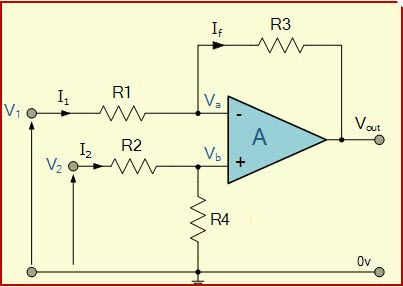

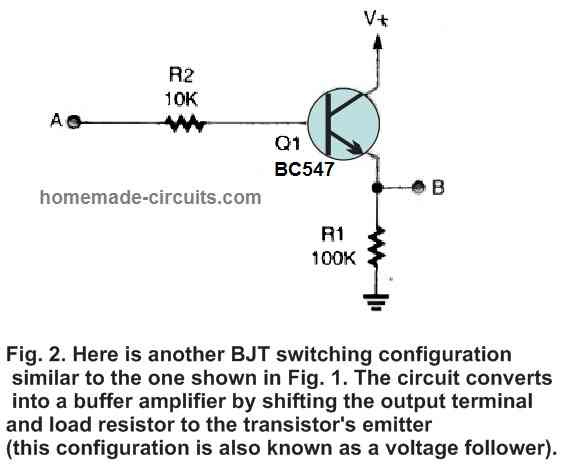

Įtampos sekiklis arba buferinis stiprintuvas yra loginio perjungimo konfigūracijos tipas, identiškas pavaizduotai 2 paveiksle. Reikėtų pažymėti, kad apkrovos rezistorius ir išėjimo gnybtas šioje grandinėje buvo perkelti iš tranzistoriaus kolektoriaus į jo emiterį, kuris yra pagrindinis skirtumas tarp šio dizaino ir pavaizduoto 1 pav.

Tranzistoriaus veikimas taip pat gali būti „apverstas“ perkeliant apkrovos rezistorių ir išvesties gnybtą į kitą BJT galą.

Kitaip tariant, kai grandinės įvesties poslinkis nepateikiamas, grandinės išėjimas išlieka mažas; tačiau kai į grandinės įvestį tiekiamas tinkamos įtampos poslinkis, grandinės išėjimas tampa didelis. (Tai yra visiškai priešinga tam, kas vyksta ankstesnėje grandinėje.)

Dviejų įėjimų loginių vartų projektavimas naudojant tranzistorius

IR vartai naudojant du tranzistorius

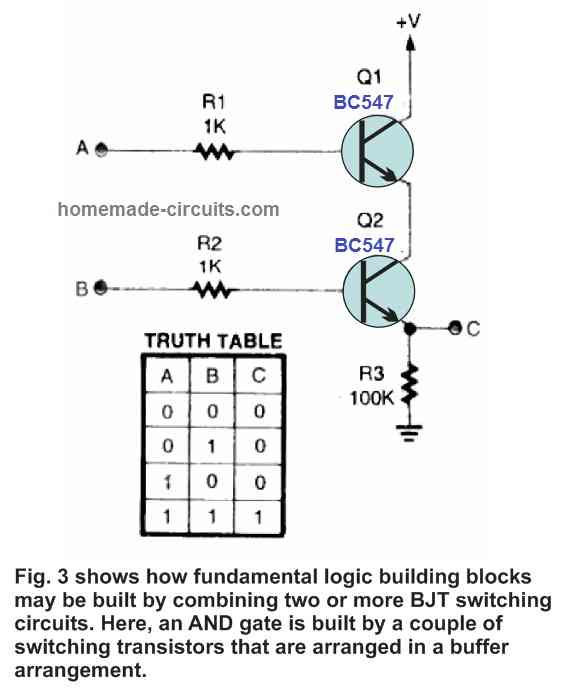

3 paveiksle parodyta, kaip galima sukurti pagrindinius dviejų įėjimų IR vartus naudojant buferių porą kartu su tų vartų tiesos lentele. Tiesos lentelė parodo, kokie būtų kiekvieno atskiro įvesties rinkinio išvesties rezultatai. Taškai A ir B naudojami kaip grandinės įėjimai, o taškas C – kaip grandinės išvestis.

Iš tiesos lentelės svarbu pažymėti, kad tik vienas įvesties parametrų rinkinys sukuria logiškai aukštą išvesties signalą, o visi kiti įvesties deriniai – logiškai žemą išvestį. 3 paveiksle pavaizduoto AND vartų išėjimas išlieka šiek tiek mažesnis už V+, kai jis pasisuka aukštai.

Taip nutinka dėl įtampos kritimo tarp dviejų tranzistorių (Q1 ir Q2).

NAND vartai naudojant du tranzistorius

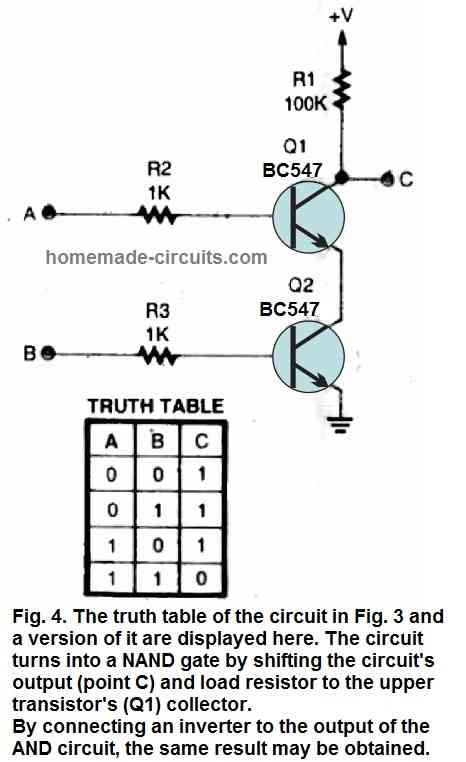

Kitas grandinės variantas 3 paveiksle ir susijusi tiesos lentelė parodyta 4 paveiksle. Grandinė virsta NEŠALAIS, perkeliant išėjimą (tašką C) ir išėjimo rezistorių į viršutinio tranzistoriaus (Q1) kolektorių.

Kadangi ir Q1, ir Q2 reikia įjungti, kad žema R1 pusė būtų įtraukta į žemę, C išėjimo įtampos nuostoliai yra nereikšmingi.

Jei tranzistoriaus IR arba tranzistoriaus NAND vartams reikia daugiau nei dviejų įėjimų, parodytuose projektuose galima prijungti daugiau tranzistorių, kad būtų sukurti trys, keturi ir tt įvesties IR arba NAND vartai.

Tačiau norint kompensuoti atskirų tranzistorių įtampos nuostolius, V+ reikėtų atitinkamai padidinti.

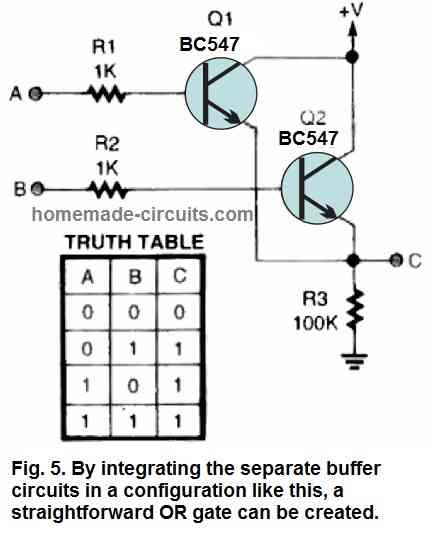

ARBA vartai naudojant du tranzistorius

Kitą loginės grandinės formą su dviem įėjimais galima pamatyti 5 paveiksle kartu su OR-vartų grandinės tiesos lentele.

Grandinės išėjimas yra didelis, kai įėjimas A arba B įėjimas yra pastumtas aukštai, tačiau dėl pakopinių tranzistorių įtampos kritimas yra didesnis nei 0,5 volto. Vėlgi, rodomi skaičiai rodo, kad yra pakankamai įtampos ir srovės, kad veiktų tolesnis tranzistorius.

NOR vartai naudojant du tranzistorius

6 paveiksle pavaizduoti kiti mūsų sąrašo vartai, dviejų įėjimų NOR vartai, kartu su jų tiesos lentele. Panašiai kaip IR ir NAND vartai reaguoja vienas į kitą, ARBA ir NOR grandinės daro tą patį.

Kiekvienas iš rodomų vartų gali tiekti pakankamai pavaros, kad suaktyvintų bent vieną ar daugiau gretimų tranzistorių vartų.

Tranzistorių loginių vartų programos

Ką darote su aukščiau pateiktomis skaitmeninėmis grandinėmis, kurias dabar turite? Viskas, ką galite pasiekti naudodami įprastinius TTL arba CMOS vartus, bet nesijaudindami dėl maitinimo įtampos apribojimų. Štai keletas tranzistorių-loginių vartų taikomųjų programų.

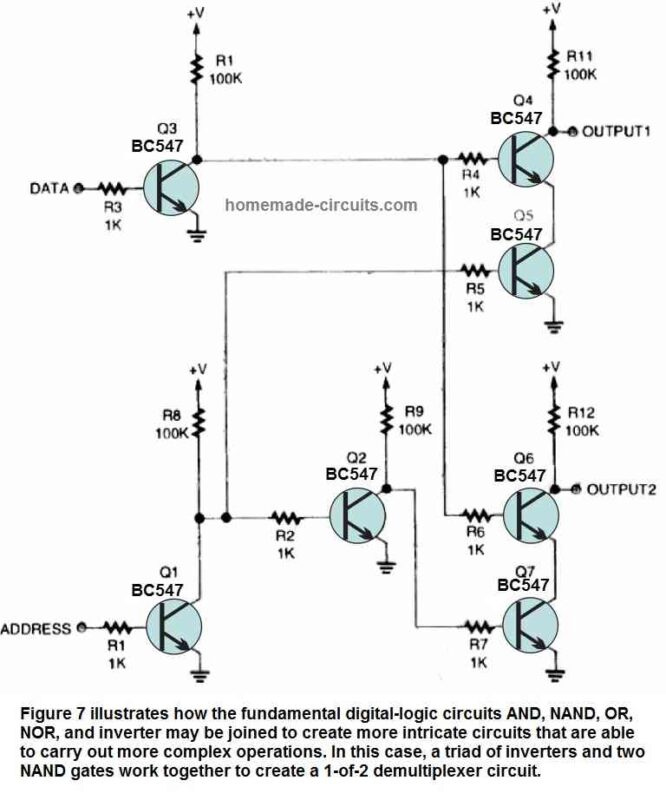

Demultiplekserio grandinė

1 iš 2 demultiplekseris su trimis NOT vartais ir dviem NAND grandinėmis parodytas 7 paveiksle. Tinkama išvestis parenkama naudojant vieno bito „adreso įvestį“, kuri gali būti OUTPUT1 arba OUTPUT2, kai taikoma vairavimo informacija. į grandinę naudojant DATA įvestį.

Grandinė veikia efektyviausiai, kai duomenų perdavimo sparta yra mažesnė nei 10 kHz. Grandinės funkcionalumas yra paprastas. Į DATA įvestį tiekiamas reikiamas signalas, kuris įjungia Q3 ir invertuoja į Q3 kolektorius gaunamus duomenis.

Q1 išėjimas yra padidinamas, jei ADDRESS įėjimas yra žemas (įžemintas arba nepateikiamas signalas). Q1 kolektorius didelė galia yra padalinta į du kelius. Pirmajame kelyje Q1 išvestis tiekiama į Q5 bazę (vieną iš dviejų įėjimų NAND vartų kojelių), įjungiant jį ir taip „aktyvinant“ NAND vartus, sudarytus iš Q4 ir Q5.

Antrajame kelyje Q1 aukšta išvestis tuo pačiu metu tiekiama į kito NOT vartų (Q2) įvestį. Atlikus dvigubą inversiją, Q2 išėjimas sumažėja. Šis žemas yra tiekiamas Q7 bazei (vienas antrojo NAND vartų gnybtas, sudarytas iš Q6 ir Q7), taip išjungiant NAND grandinę.

Bet kokia DATA įvesties informacija arba signalas tokiomis aplinkybėmis patenka į OUTPUT1. Arba situacija pasikeičia, jei į ADDRESS įvestį duodamas aukštas signalas. Reiškia, bet kokia grandinei pateikta informacija bus rodoma OUTPUT2, nes Q4/Q5 NAND vartai yra išjungti, o Q6/Q7 NAND vartai įjungti.

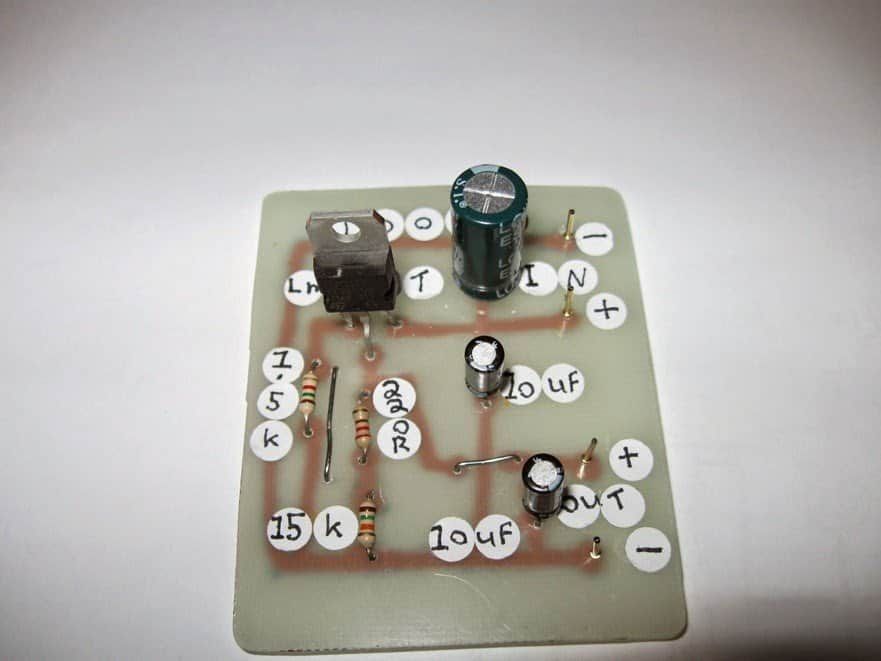

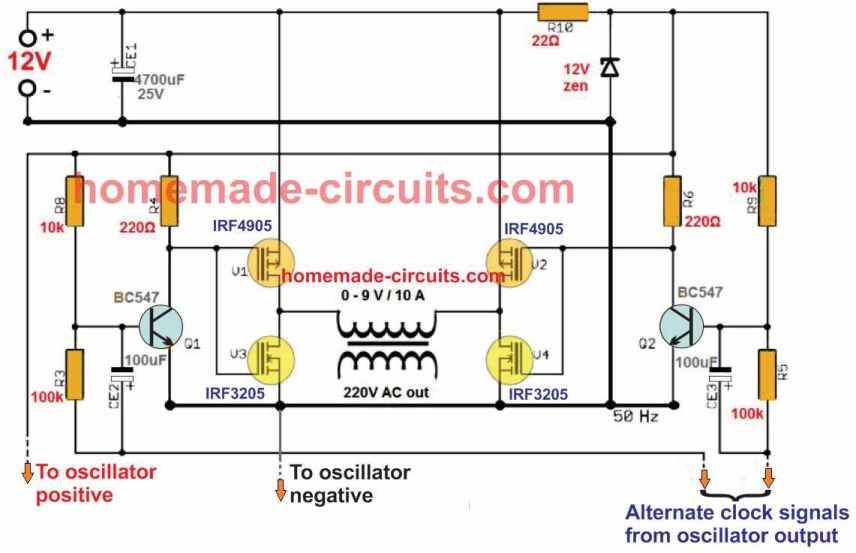

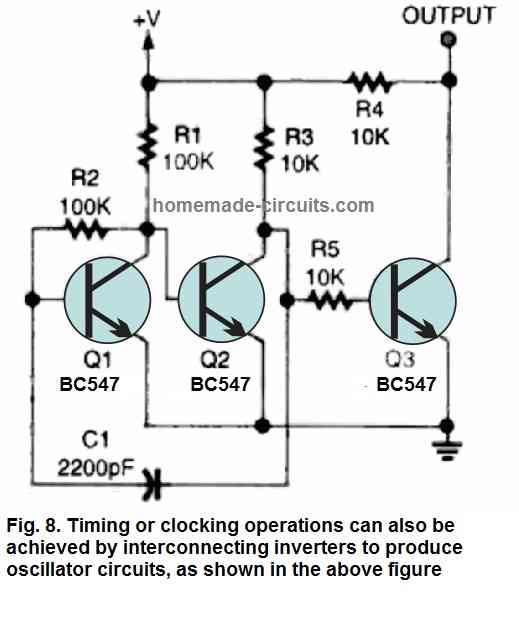

Osciliatoriaus grandinė (laikrodžio generatorius)

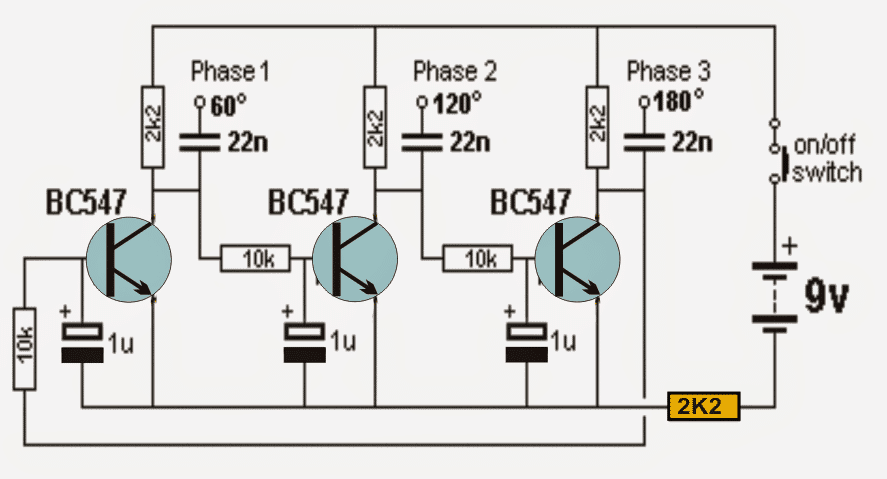

Kita mūsų tranzistoriaus loginių užtvarų programa, parodyta 8 pav., yra pagrindinis laikrodžio generatorius (taip pat žinomas kaip osciliatorius), pagamintas iš trijų įprastų NOT vartų keitiklių (vienas iš jų yra pakreiptas naudojant grįžtamojo ryšio rezistorių R2, kuris jį įjungia analogiškame regione).

Norint išvesti kvadratą, yra įtrauktas trečiasis NOT užtvaras (Q3), suteikiantis osciliatoriaus išėjimo papildymą. C1 vertę galima padidinti arba sumažinti, kad būtų pakeistas grandinės veikimo dažnis. Išvesties bangos formos dažnis yra maždaug 7 kHz, kai V+ esant 1,5 volto nuolatinei įtampai, naudojant nurodytas komponentų vertes.

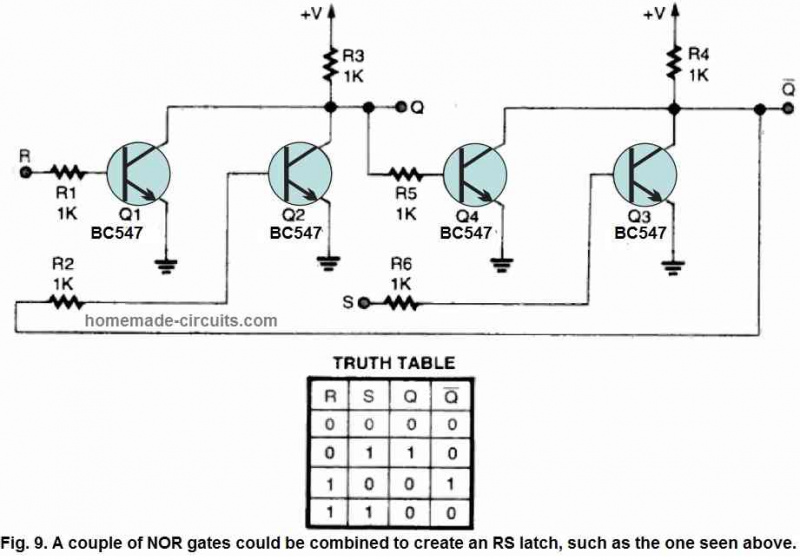

RS užrakto grandinė

9 pav. parodyta mūsų galutinė taikymo grandinė, RS skląstis, sudarytas iš dviejų NOR vartų. Siekiant užtikrinti sveiką išėjimo pavarą Q ir Q išėjimuose, rezistoriai R3 ir R4 sureguliuoti iki 1k omų.

RS skląsčio tiesos lentelė rodoma kartu su schema. Tai tik keletas iliustracijų apie keletą patikimų žemos įtampos skaitmeninių loginių vartų grandinių, kurios gali būti sukurtos naudojant atskirus tranzistorius.

Grandinėms, naudojančioms tranzistorinę logiką, reikia per daug dalių

Daugelį problemų galima išspręsti naudojant visas šias žemos įtampos tranzistorines logines grandines. Tačiau naudojant per daug šių tranzistorinių vartų gali kilti naujų problemų.

Tranzistorių ir rezistorių skaičius gali būti gana didelis, jei jūsų kuriamoje programoje yra daug vartelių, užimančių vertingą erdvę.

Vienas iš būdų išspręsti šią problemą yra naudoti tranzistorių matricas (daugelis tranzistorių yra įdėtos į plastiką) ir SIP (vieno vidinio paketo) rezistorius vietoj atskirų blokų.

Aukščiau pateiktas metodas gali sutaupyti toną vietos ant PCB, išlaikant našumą, prilygstantį jų viso dydžio ekvivalentams. Tranzistorių matricos siūlomos ant paviršiaus montuojamų, 14 kontaktų per skylę ir keturių paketų pakuotėse.

Daugumoje grandinių tranzistorių tipų maišymas gali būti gana priimtinas.

Nepaisant to, patartina, kad eksperimentuotojas dirbtų su vieno tipo tranzistoriumi, kad sukurtų tranzistorines logines grandines (tai reiškia, kad jei kuriate vartų sekciją naudodami BC547, tada pabandykite naudoti tą patį BJT ir kitiems likusiems vartams).

Priežastis yra ta, kad įvairūs tranzistorių variantai gali turėti šiek tiek skirtingas savybes ir todėl gali elgtis skirtingai.

Pavyzdžiui, kai kurių tranzistorių bazinė įjungimo riba gali būti didesnė arba mažesnė nei kito, arba bendras srovės stiprinimas gali būti šiek tiek didesnis arba mažesnis.

Kita vertus, vieno tipo tranzistoriaus masinės dėžutės pirkimo kaina taip pat gali būti mažesnė. Jūsų grandinių našumas padidės, jei jūsų loginiai vartai bus sukurti naudojant atitinkamus tranzistorius, o visas projektas galiausiai bus naudingesnis.