Kombinuotose grandinėse skirtingi loginiai vartai naudojami kuriant kodavimo įrenginį, multiplekserį, dekoderį ir multiplekserį. Šios grandinės turi tam tikrų savybių, pavyzdžiui, šios grandinės išvestis daugiausia priklauso nuo lygio, kuris bet kuriuo metu yra įėjimo gnybtuose. Ši grandinė neapima jokios atminties. Ankstesnė įvesties būsena neturi jokios įtakos dabartinei šios grandinės būsenai. Kombinuotos grandinės įėjimai ir išėjimai yra „n“ ne. įvesties & ‘m’ Nr. rezultatų. Kai kurios kombinuotos grandinės yra pusiau ir pilnai sujungtos, atimančios, koduojančios, dekoduojančios, multiplekserinės ir demultiplekserės. Šiame straipsnyje aptariama pusinio ir visiško papildymo apžvalga ir jis dirba su tiesos lentelėmis.

Kas yra „Adder“?

Papildiklis yra a skaitmeninės logikos grandinė elektronikoje, kuri plačiai naudojama skaičiams pridėti. Daugelyje kompiuterių ir kitų tipų procesorių priedai netgi naudojami adresams ir susijusioms veikloms apskaičiuoti bei lentelių indeksams apskaičiuoti ALU ir netgi naudojami kitose procesorių dalyse. Tai gali būti sukurta daugybei skaitinių vaizdų, pvz., Perteklius-3 arba dvejetainis koduotas dešimtainis skaičius. Priedai iš esmės skirstomi į du tipus: „Pusė papildymo“ ir „Pilna suma“.

Kas yra „Halder Adder“ ir „Full Adder Circuit“?

Pusės sumavimo grandinėje yra du įėjimai: A ir B, kurie prideda du įvesties skaitmenis ir sukuria nešimą ir sumą. Visoje sumavimo grandinėje yra trys įėjimai: A ir C, kurie prideda tris įvesties skaičius ir sukuria nešimą ir sumą. Šiame straipsnyje pateikiama išsami informacija apie tai, koks yra pusės papildymo tikslas ir visas priedas lentelėse ir net schemose. Jau minėta, kad pagrindinis ir esminis pridėtojų tikslas yra papildymas. Žemiau pateikiama išsami informacija pusės sumuotojo ir pilnosios sumos teorija.

Pagrindinis pusiau ir pilnai

Pusė Adderio

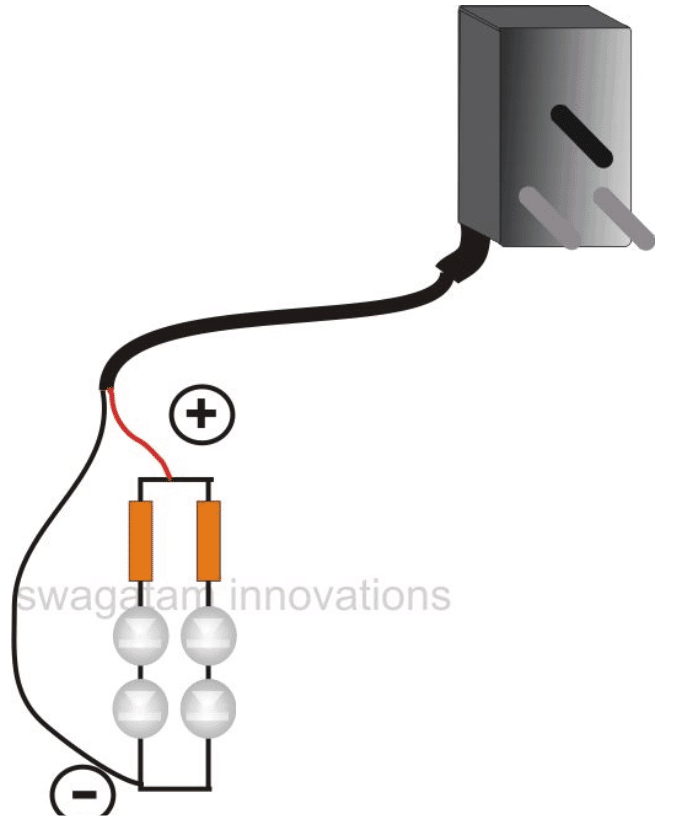

Taigi, atėjęs prie pusės sumavimo scenarijaus, jis prideda du dvejetainius skaitmenis, kur įvesties bitai vadinami padidinimu ir pridėjimu, o rezultatas bus du išėjimai, vienas yra suma, o kitas yra nešimas. Norėdami atlikti suminę operaciją, XOR taikomas abiem įėjimams, o AND vartai - abiem įėjimams, kad būtų sukurtas nešimas.

HA funkcinė schema

Visoje sumavimo grandinėje jis prideda 3 vieno bitų skaičius, kur du iš trijų bitų gali būti vadinami operandais, o kiti - kaip nešami bitai. Pagaminta išvestis yra 2 bitų išvestis ir juos galima nurodyti to kaip produkcijos nešiojimas ir suma.

Naudodami pusiau sumontuotą elementą, jūs galite suprojektuoti paprastą papildymą loginių vartų pagalba.

Pažiūrėkime dviejų atskirų bitų pridėjimo pavyzdį.

2 bitų pusės sumaišties tiesos lentelė yra toks kaip žemiau:

Pusės papildomos tiesos lentelė

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

Tai yra mažiausiai galimi vieno bitų deriniai. Bet 1 + 1 rezultatas yra 10, suminis rezultatas turi būti perrašytas kaip 2 bitų išvestis. Taigi lygtis galima parašyti kaip

0 + 0 = 00

0 + 1 = 01

1 + 0 = 01

1 + 1 = 10

Rezultatas „1“ iš „10“ yra vykdymas. „SUM“ yra įprasta išvestis, o „CARRY“ - atlikimas.

Dabar paaiškėjo, kad 1 bitų sumavimo priemonę galima lengvai įdiegti naudojant „XOR Gate“ išvesties „SUM“ ir „AND Gate“, skirtos „Carry“.

Pvz., Kai reikia pridėti du 8 bitų baitus kartu, tada jį galima įgyvendinti naudojant visos sumos logikos grandinę. Pusės sumavimo funkcija naudinga, kai norite pridėti vieną dvejetainį skaičių.

Dviejų dvejetainių skaitmenų pridėtojų kūrimo būdas būtų sudaryti tiesos lentelę ir ją sumažinti. Kai norite sudaryti trijų dvejetainių skaitmenų skaičių, pusės papildymo operacija atliekama du kartus. Panašiai, kai nusprendžiate padaryti keturženklį papildymą, operacija atliekama dar kartą. Remiantis šia teorija buvo aišku, kad įgyvendinimas yra paprastas, tačiau kūrimas yra laiko reikalaujantis procesas.

Paprasčiausia išraiška naudoja išskirtinę OR funkciją:

Suma = A XOR B

Nešiotis = A IR B

HA loginė schema

Ir lygiavertė išraiška, kalbant apie pagrindinius AND, OR ir NOT, yra:

SUM = A.B + A.B ’

Pusės papildytojo VHDL kodas

Esybė ha yra

Uostas (a: STD_LOGIC

b: STD_LOGIC

sha: iš STD_LOGIC

cha: iš STD_LOGIC)

pabaigos ha

Architektūra Minėtos grandinės elgesys yra

pradėti

sha<= a xor b

ne<= a and b

pabaigos elgesys

Pusės skaitiklio IC numeris

Pusės sumaišytojo diegimas gali būti atliekamas per didelės spartos CMOS skaitmeninės logikos integruotąsias grandines, tokias kaip 74HCxx serija, į kurią įeina SN74HC08 (7408) ir SN74HC86 (7486).

Pusės sumaišytojo apribojimai

Pagrindinė priežastis vadinti šiuos dvejetainius pridėtinius kaip „Half Adders“ yra ta, kad nėra diapazono, kuriame būtų naudojamas nešimo bitas naudojant ankstesnį bitą. Taigi, tai yra pagrindinis HA apribojimas, kuris kadaise buvo naudojamas kaip dvejetainis skaitiklis, ypač realiuoju laiku, kai reikia pridėti kelis bitus. Taigi šį apribojimą galima įveikti naudojant visus pridėtinius.

Visiškas papildymas

Šį papildinį sunku įgyvendinti, lyginant su pusiau papildančiu.

Funkcinė pilno papildymo schema

Pusiau sumaišyto ir pilno papildymo skirtumas yra tas, kad pilnasis skaitiklis turi tris įvestis ir dvi išvestis, o pusė papildytuvo turi tik dvi įvestis ir dvi išvestis. Pirmieji du įėjimai yra A ir B, o trečiasis įėjimas yra įvesties nešimas kaip C-IN. Kai suprojektuojama visos sumos logika, sureguliuokite aštuonis iš jų, kad sukurtumėte viso baito plitimo koeficientą, ir perkraukite nešiojamąjį bitą iš vieno papildymo į kitą.

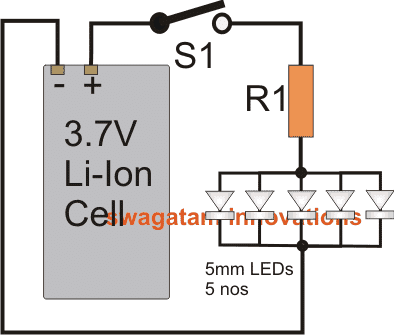

FA tiesos lentelė

Išvesties nešimas žymimas kaip C-OUT, o įprastas išėjimas - kaip S, kuris yra „SUM“.

Su aukščiau visa papildymo tiesos lentelė , visos sumavimo grandinės įgyvendinimą galima lengvai suprasti. SUM „S“ gaminamas dviem etapais:

- XOR sukurdami pateiktas įvestis „A“ ir „B“

- Tada A XOR B rezultatas yra XOR su C-IN

Tai sukuria SUM ir C-OUT yra teisinga tik tada, kai du iš trijų įėjimų yra HIGH, tada C-OUT bus HIGH. Taigi, mes galime įgyvendinti visą sumavimo grandinę dviejų pusių sumaišytųjų grandinių pagalba. Iš pradžių pusė sumaišytoji bus naudojama pridėti A ir B dalinei sumai gauti, o antrosios pusės papildymo logika gali būti naudojama pridėjus C-IN prie sumos, kurią sukuria pirmosios pusės papildytojas, kad gautų galutinę S išvestį.

Jei kuri nors iš pusės papildymo logikos sukuria nešiojimą, bus išvesties nešimas. Taigi, C-OUT bus OR-funkcija iš pusiau sumaišytų „Carry“ išėjimų. Pažvelkite į žemiau nurodytą visos sumavimo grandinės įgyvendinimą.

Pilna papildytojo loginė schema

Didesnių loginių schemų įgyvendinimas yra įmanomas naudojant aukščiau pateiktą visiško sumavimo logiką, operacijai vaizduoti dažniausiai naudojamas paprastesnis simbolis. Žemiau pateikiamas paprastesnis vieno bitų viso sumavimo schema.

Naudodami tokio tipo simbolius, galime susieti du bitus, paimdami nešiojimą iš kitos mažesnės vertės ir siunčiant perkėlimą į kitą didesnę. Kompiuteryje, norint atlikti kelių bitų operaciją, kiekvienas bitas turi būti nurodytas visu skaitikliu ir turi būti pridėtas vienu metu. Taigi, norint pridėti du 8 bitų numerius, jums reikės 8 pilnų pridėtinių, kuriuos galima suformuoti pakopomis du iš 4 bitų blokų.

Pusė papildytojo ir pilnoji suma, naudojant „K-Map“

Net sumą ir rezultatą pusei sumaišytojo taip pat galima gauti naudojant Karnaugh žemėlapio (K-map) metodą. pusė sumaišytojo ir pilnutinė loginė išraiška galima gauti per K-map. Taigi, šių pridėtojų K žemėlapis aptariamas toliau.

Pusės sumaišytojo K žemėlapis yra

HA K žemėlapis

Pilnas papildymo „K-Map“ yra

FA K žemėlapis

Loginė SUM ir Carry išraiška

Loginę sumos (S) išraišką galima nustatyti remiantis įvestimis, paminėtomis lentelėje.

= A’B’Cin + A ’B CCin’ + A B’Cin ’+ AB Cin

= Cin (A’B ’+ AB) + Cin’ (A’B + A B ’)

= Cin EX-OR (A EX-OR B)

= (1,2,4,7)

Loginę nešimo (Cout) išraišką galima nustatyti pagal lentelėje nurodytus įvestis.

= A’B Cin + AB’Cin + AB Cin ’+ ABCin

= AB + BCin + ACin

= (3, 5, 6, 7)

Naudodamiesi minėtomis tiesos lentelėmis, rezultatus galite gauti ir procedūra yra tokia:

Kombinuota grandinė sujungia skirtingus grandinės vartus, kur jie gali būti koduotojas, dekoderis, multiplekseris ir demultiplekseris . Kombinuotų grandinių charakteristikos yra šios.

- Išvestis bet kuriuo momentu yra pagrįsta tik lygiais, esančiais įvesties gnybtuose.

- Jis nenaudoja jokios atminties. Ankstesnė įvesties būsena neturi jokios įtakos dabartinei grandinės būsenai.

- Jis gali turėti bet kokį įėjimų skaičių ir m išėjimų skaičių.

VHDL kodavimas

VHDL kodavimas visam papildymui įtraukti šiuos dalykus.

esmė full_add yra

Uostas (a: STD_LOGIC

b: STD_LOGIC

cin: STD_LOGIC

suma: iš STD_LOGIC

cout: iš STD_LOGIC)

pabaiga full_add

Architektūra full_add elgsena yra

komponentas ha yra

Uostas (a: STD_LOGIC

b: STD_LOGIC

sha: iš STD_LOGIC

cha: iš STD_LOGIC)

pabaigos komponentas

signalas s_s, c1, c2: STD_LOGIC

pradėti

HA1: ha uosto žemėlapis (a, b, s_s, c1)

HA2: ha uosto žemėlapis (s_s, cin, summa, c2)

išlaidų<=c1 or c2

pabaigos elgesys

skirtumas tarp pusės ir visos sumos yra tai, kad pusė sumaišytojo duoda rezultatų, o pilnasis sumaišytojas naudoja pusę sumaišytojo, kad gautų kitokį rezultatą. Panašiai, nors „Full-Adder“ yra du „Half-Adders“, „Full-Adder“ yra tikrasis blokas, kurį naudojame kurdami aritmetines grandines.

Nešiokite „Lookahead Adders“

Turint mintyje banginių nešiklių sumontavimo grandines, bitai, kurie yra būtini papildymui, yra iš karto prieinami. Kiekvienam papildymo skyriui reikia numatyti savo laiką, kol atkeliaus nešimas iš ankstesnio papildymo bloko. Dėl to SUM ir CARRY sukūrimas užima daugiau laiko, nes kiekvienas grandinės skyrius laukia įvesties.

Pavyzdžiui, norėdamas pateikti išvestį n -tajam blokui, jis turi gauti įvestį iš (n-1)-ojo bloko. Ir šis vėlavimas atitinkamai vadinamas sklidimo vėlavimu.

Siekiant įveikti pulsacijos nešiklio vėlavimą, buvo įvestas nešiojamojo žvilgsnio papildiklis. Čia, naudojant sudėtingą aparatinę įrangą, sklaidos vėlavimą galima sumažinti. Žemiau pateiktoje schemoje parodytas nešiojimo žvilgsnio papildiklis, naudojant visus priedus.

Nešiokite žvilgsnį naudodami „Full Adder“

Tiesos lentelė ir atitinkamos išvesties lygtys yra

| Į | B | C | C + 1 | Būklė |

| 0 | 0 | 0 | 0 | Nešiotis Generuoti |

| 0 | 0 | 1 | 0 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 1 | Nešiotis Dauginti |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 1 | Nešiotis Generuoti |

| 1 | 1 | 1 | 1 |

Nešimo sklidimo lygtis yra Pi = Ai XOR Bi, o nešimo generatorius yra Gi = Ai * Bi. Naudojant šias lygtis, suma ir nešimo lygtys gali būti pavaizduotos kaip

SUM = Pi XOR Ci

Ci + 1 = Gi + Pi * Ci

Gi pateikia nešimą tik tada, kai abu įėjimai Ai ir Bi yra 1, neatsižvelgiant į įvesties nešimą. Pi yra susijęs su nešimo plitimu nuo Ci iki Ci + 1.

Skirtumas tarp Half Adder ir Full Adder

skirtumas tarp pusės ir visos suminės lentelės yra parodyta žemiau.

| Pusė Adderio | Visiškas papildymas |

| „Half Adder“ (HA) yra kombinuota loginė grandinė ir ši grandinė naudojama dviem vieno bitų skaitmenims pridėti. | „Full Adder“ (FA) yra kombinuota grandinė ir ši grandinė naudojama trims vieno bitų skaitmenims pridėti. |

| HA atveju, sukėlus ankstesnį papildymą, jo negalima pridėti prie kito žingsnio. | FA, kai nešimas generuojamas iš ankstesnio pridėjimo, tada jį galima pridėti prie kito žingsnio. |

| Pusę sumaišytojo sudaro du loginiai vartai, tokie kaip AND vartai ir EX-OR vartai. | Visą papildymą sudaro du EX-OR vartai, du OR vartai ir du AND vartai. |

| Pusės sumaišytojo įvesties bitai yra du kaip A, B. | Įvesties bitai visoje sumoje yra trys, pavyzdžiui, A, B ir C-in |

| Pusės suminės sumos ir nešimo lygtis yra S = a⊕b C = a * b | Pilna papildymo logikos išraiška yra S = a ⊕ b⊕Cin Cout = (a * b) + (Cin * (a⊕b)). |

| HA naudojama kompiuteriuose, skaičiuotuvuose, prietaisuose, naudojamuose skaitmeniniam matavimui ir kt. | FA naudojamas skaitmeniniuose procesoriuose, daugybinių bitų pridėjime ir kt. |

pagrindiniai skirtumai tarp pusės ir visos sumos yra aptariami toliau.

- Pusės sumuotojas sugeneruoja sumą ir nešiojimą, pridėdamas du dvejetainius įvestis, o pilnasis skaitiklis naudojamas sumai ir nešiojimui generuoti pridedant tris dvejetainius įėjimus. Pusinės sumos ir visos suminės aparatinės įrangos architektūra nėra ta pati.

- Pagrindinis bruožas, išskiriantis HA ir FA, yra tas, kad HA nėra tokio sandorio, kuris apsvarstytų paskutinį papildymą kaip jo indėlis. Tačiau FA suranda tam tikrą įvesties stulpelį, pvz., „Cin“, kad apsvarstytų paskutinio papildymo nešimo bitą.

- Du priedai parodys skirtumą, atsižvelgiant į komponentus, naudojamus grandinėje jo statybai. Pusiniai priedai (HA) suprojektuoti derinant du loginius vartus, pvz., AND & EX-OR, o FA yra sukurtas derinant tris AND, du XOR ir vieną OR vartus.

- Iš esmės HA veikia su dviem dviem 1 bitų įėjimais, o FA veikia su trim 1 bitų įėjimais. Pusė sumadiklio naudojama skirtinguose elektroniniuose įtaisuose vertinant pridėjimą, o pilnasis skaitiklis naudojamas skaitmeniniuose procesoriuose, norint pridėti ilgą bitą.

- Šių dviejų priedų panašumai yra tokie: HA ir FA yra kombinuotos skaitmeninės grandinės, todėl nenaudoja jokių atminties elementų, tokių kaip nuoseklios grandinės. Šios grandinės yra būtinos aritmetinei operacijai, kad būtų pridėtas dvejetainis skaičius.

Visas „Adder“ įgyvendinimas naudojant „Half Adders“

FA gali būti įgyvendinamas per du logiškai sujungtus papildinius. Blokinė to schema gali būti parodyta žemiau, kurioje nurodoma FA jungtis naudojant du pusinius pridėtinius.

Ankstesnių skaičiavimų suma ir nešimo lygtys yra

S = A ‘B’ Cin + A ’BC’ + ABCin

Cout = AB + ACin + BCin

Sumos lygtį galima parašyti taip.

„Cin“ (A’B ‘+ AB) + C’ (A‘B + A B ’)

Taigi, suma = Cin EX-OR (A EX-OR B)

Cin (A EX-OR B) + C’in (A EX-OR B)

= Cin EX-OR (A EX-OR B)

Coutas gali būti parašytas taip.

COUT = AB + ACin + BCin.

Cout = AB + + nusivylimų BCin (A + A)

= ABCin + AB + ACin + A ’B Cin

= AB (1 + Cin) + ACin + A ’B Cin

= A B + ACin + A ’B Cin

= AB + ACin (B + B ’) + A’ B Cin

= ABCin + AB + A’B Cin + A ’B Cin

= AB (Cin + 1) + A B Cin + A ’B Cin

= AB + AB ’Cin + A’ B Cin

= AB + Cin (AB ’+ A’B)

Todėl COUT = AB + Cin (A EX-OR B)

Atsižvelgiant į pirmiau pateiktas dvi sumas ir nešimo lygtis, FA grandinę galima įgyvendinti dviejų HA ir OR vartų pagalba. Aukščiau pavaizduota pilno sumaišytojo su dviem pusėmis papildų schema.

Pilnas papildiklis, naudojant du pusinius priedus

Visas „Adder Design“ dizainas naudojant NAND vartus

NAND vartai yra vienos rūšies universalūs vartai, naudojami bet kokiam loginiam dizainui vykdyti. FA grandinė su NAND vartų schema parodyta žemiau.

FA naudojant NAND Gates

FA yra lengvas vieno bitų papildiklis ir jei mes norime atlikti n bitų pridėjimą, tada n ne. vieno bitų FA turi būti naudojami kaskados ryšio formatu.

Privalumai

pusės ir visos sumos pranašumų privalumai įtraukti šiuos dalykus.

- Svarbiausias pusės papildytuvo tikslas yra pridėti du vieno bitų skaičius

- Visiškai sudedamieji turi galimybę pridėti nešiojimo bitą, kuris atsiranda dėl ankstesnio pridėjimo

- Turint pilną sumavimo priemonę, gali būti įdiegtos tokios svarbios grandinės kaip papildiklis, multiplekseris ir daugelis kitų

- Visos sumavimo grandinės sunaudoja minimaliai energijos

- Pilnojo, o ne pusės, pliuso privalumai yra tai, kad pilnasis papildiklis naudojamas įveikti pusės papildymo trūkumą, nes pusiau sumaišytojas daugiausia naudojamas dviem 1 bitų skaičiams pridėti. Pusė pridėtojų neprideda nešiojimo antgalio, todėl norint įveikti šį pilną skaičių, naudojamasi. Naudojant „Full adder“, galima pridėti tris bitus ir generuoti du išėjimus.

- Priedų projektavimas yra paprastas ir tai yra pagrindinė sudedamoji dalis, kad būtų galima lengvai suprasti vieno bito priedą.

- Pridėjus keitiklį, šią sumą galima konvertuoti į pusę atimties.

- Naudojant pilną sumą, galima gauti didelę galią.

- Didelis greitis

- Labai stiprus maitinimo įtampos mastelis

Trūkumai

pusės ir pilno sumavimo trūkumai įtraukti šiuos dalykus.

- Be to, pusė sumaišytojo negali būti naudojama prieš nešant, todėl ji netaikoma daugiapakopio pridėjimo pakopai.

- Norint įveikti šį trūkumą, FA reikia pridėti tris 1 bitą.

- Kai FA naudojamas grandinės pavidalu, pavyzdžiui, RA (Ripple Adder), tada gali sumažėti išvesties pavaros galimybė.

Programos

Pusės ir pilnosios sumos taikikliai apima šiuos dalykus.

- Dvejetainių bitų pridėjimą gali atlikti pusė sumaišytojo, naudodama ALU kompiuteryje, nes jis naudoja sumuotoją.

- Pusės sumaišytojo derinys gali būti naudojamas suprojektuoti pilną sumavimo grandinę.

- Pusė skaičiuotuvų naudojami skaičiuoklėse ir adresams bei lentelėms matuoti

- Šios grandinės naudojamos skirtingoms skaitmeninių grandinių programoms tvarkyti. Ateityje ji vaidina pagrindinį vaidmenį skaitmeninėje elektronikoje.

- FA grandinė naudojama kaip elementas daugelyje didelių grandinių, tokių kaip „Ripple Carry Adder“. Šis papildiklis vienu metu prideda bitų skaičių.

- FA naudojami aritmetinės logikos vienete (ALU)

- FA yra naudojami su grafika susijusiose programose, tokiose kaip GPU (grafikos procesorius)

- Jie naudojami daugybos grandinėje, kad būtų įvykdytas „Carryout Multiplication“.

- Kompiuteryje, norint sugeneruoti atminties adresą ir sukurti programos priešinį tašką, kad būtų galima atlikti tolesnius nurodymus, Aritmetinės logikos vienetas naudojamas naudojant „Pilnus priedus“.

Taigi, pridėjus du dvejetainius skaičius, skaitmenys iš pradžių pridedami mažiausiai. Šį procesą galima atlikti per pusę sumaišytojo, nes paprasčiausias n / w, leidžiantis pridėti du 1 bitų skaičius. Šio papildiklio įvestys yra dvejetainiai skaitmenys, o išvestys yra suma (S) ir nešimas (C).

Kai įtraukiamas skaitmenų skaičius, HA tinklas naudojamas paprasčiausiai sujungti mažiausiai skaitmenų, nes HA negali pridėti ankstesnės klasės nešiojimo numerio. Visą skaitmeninę sumą galima apibrėžti kaip visų skaitmeninių aritmetikos įtaisų pagrindą. Tai naudojama trims 1 skaitmenų skaičiams pridėti. Šis papildiklis apima tris įvestis, tokias kaip A, B ir Cin, o išvestys yra Sum ir Cout.

Susijusios sąvokos

sąvokos, susijusios su pusė ir visa suma tik nesilaikykite vieno tikslo. Jie plačiai naudojami daugelyje programų ir paminėti keli susiję dalykai:

- Pusės suminės ir visos suminės sumos IC numeris

- 8 bitų papildiklio kūrimas

- Kokios yra pusės papildomos atsargumo priemonės?

- JAVA Ripple Carry Adder programėlė

Todėl visa tai yra apie pusės sumuotojo ir pilnosios sumos teorija kartu su tiesos lentelėmis ir loginėmis schemomis taip pat parodytas visiško sumaišytojo, naudojant pusę papildymo grandinės, dizainas. Daugelis pusė sumaišytojo ir pilnojo papildymo pdf yra dokumentų, kuriuose pateikiama išsami informacija apie šias sąvokas. Be to, svarbu žinoti kaip įgyvendinamas 4 bitų pilnas papildiklis ?