8085 mikroprocesorius yra vienos rūšies puslaidininkinis įtaisas sinchronizuojamas CLK (laikrodis). Šis procesorius gali būti sukonstruotas naudojant elektronines logines grandines, pagamintas naudojant tokias technologijas kaip VLSI (labai didelio masto integracija) arba LSI (didelio masto integracija). Pagrindinė mikroprocesoriaus funkcija yra atlikti keletą funkcijų, taip pat priimti sprendimus dėl programos įgyvendinimo serijos keitimo. Kompiuteriuose centrinis procesorius bus vykdomas vienoje ar papildomose plokštėse, kad būtų atliktos skaičiavimo užduotys. Rinkoje yra įvairių tipų mikroprocesorių, tokių kaip procesorius, apima loginę schemą, valdymo bloką ir jį galima suskirstyti į tris segmentus, tokius kaip ALU, valdymo blokas ir registrų masyvas.

Kas yra 8085 mikroprocesorius?

8085 m mikroprocesorius yra 8 bitų bendrosios paskirties procesorius kad gali susitvarkyti su 64K baitų atmintimi. Šis mikroprocesorius susideda iš 40 kontaktų, taip pat veikia su + 5V maitinimo šaltinis . Šis procesorius gali dirbti maksimaliu 3MHz dažniu. Šis procesorius yra trijų versijų, tokių kaip 8085 AH, 8085 AH1 ir 8085 AH2, sukurtos naudojant HMOS technologiją. Labai išvystytos versijos sunaudoja 20% maitinimo šaltinio. Šio procesoriaus versijų CLK dažniai yra 8085 A-3 MHz, 8085AH-3 MHz, 8085 AH2-5 MHz ir 8085 AH1-6 MHz.

8085 mikroprocesorius

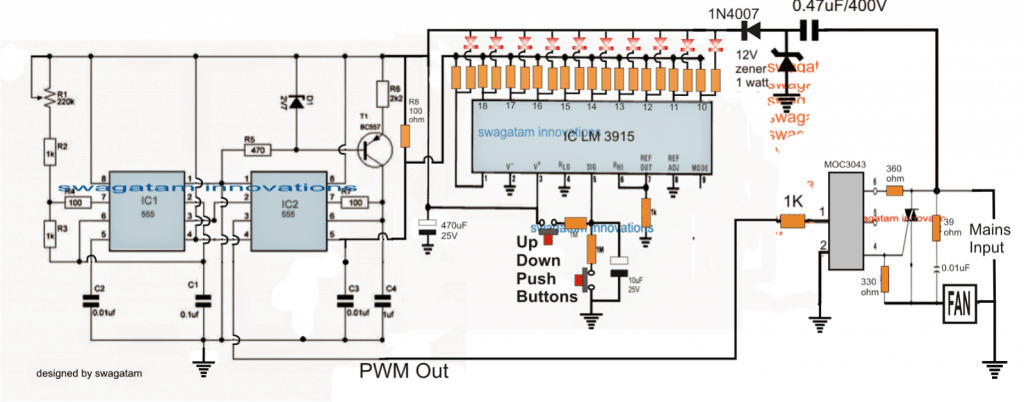

8085 mikroprocesoriaus kaiščių konfigūracija

40 smeigtukų mikroprocesorius galima suskirstyti į šešias grupes, tokias kaip adreso magistralė, duomenų magistralė, valdymo signalai ir būsenos signalai, maitinimo šaltinis ir dažnis, išoriškai paleisti signalai ir nuoseklūs įvesties / išvesties prievadai.

8085 Mikroprocesoriaus kaiščių konfigūracija

Adreso magistralė (A8-A15)

Adreso magistralės smeigtukai svyruoja nuo A8 iki A15 ir jie daugiausia taikomi didžiausiam atminties adreso bitui.

Adreso magistralė (arba) duomenų magistralė (AD0-AD7)

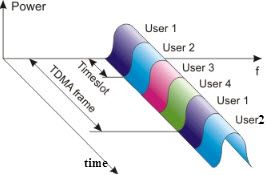

Adreso magistralės arba duomenų magistralės smeigtukai yra nuo AD0 iki AD7, ir šie smeigtukai taikomi pirminio aparato CLK ciklo adreso magistralės LSB (mažiausiai reikšmingi bitai), taip pat naudojami kaip duomenų magistralė antram laikrodžio ciklui & trečiasis laikrodžio ciklas.

CLK ciklas gali būti suprojektuotas kaip laikas, esantis tarp dviejų netoliese esančių osciliatoriaus impulsų, arba tiesiog jis gali būti nulinis voltų. Pirmasis laikrodis yra pagrindinis impulsų diapazonų perėjimas nuo 0 V iki 5 V ir tada pasiekia 0 V.

Įjungti adreso užraktą (ALE)

Iš esmės ALE padeda išardyti duomenų magistralę ir žemo užsakymo adresą. Tai bus didelis per pagrindinį laikrodžio ciklą, taip pat leis adresų bitai su maža tvarka. Adreso magistralė su maža tvarka pridedama atminčiai, kitaip bet koks išorinis užraktas.

Būsenos signalas (IO / 1000)

Būsenos signalas IO / M išsprendžia, ar adresas skirtas atmintis, ar įvestis / išvestis. Kai adresas yra didelis, adreso magistralės adresas naudojamas įvesties / išvesties įrenginių įtaisams. Kai adresas yra mažas, atmintyje naudojamas adreso magistralės adresas.

Būsenos signalai (S0-S1)

Būsenos signalai S0, S1 suteikia skirtingas funkcijas, taip pat būseną, atsižvelgiant į jų būseną.

- Kai S0, S1 yra 01, operacija bus HALT.

- S0, S1 yra 10, tada operacija bus RAŠYTA

- Kai S0, S1 yra 10, operacija bus SKAITYTA

- Kai S0, S1 yra 11, operacija bus FETCH

Aktyvus žemas signalas (RD)

RD yra energinis žemas signalas ir operacija atliekama, kai indikacija tampa maža, ir ji naudojama mikroprocesoriaus READ veikimui valdyti. Kai RD kaištis tampa mažas, 8085 mikroprocesorius supranta informaciją iš įvesties / išvesties įrenginio ar atminties.

Aktyvus žemas signalas (WR)

Tai energinis žemas signalas, ir jis valdo mikroprocesoriaus rašymo operacijas. Kai tik WR kaištis bus mažas, informacija bus įrašyta į įvesties / išvesties įrenginį arba atmintį.

PARUOŠTA

„READY“ kaištis naudojamas kartu su mikroprocesoriumi 8085, kad būtų užtikrinta, ar įrenginys nustatytas priimti ar perduoti duomenis. Prietaisas gali būti A / D keitiklis, LCD ekranas ir pan. Šie įrenginiai yra susieti su 8085 mikroprocesoriumi su „READY“ kaiščiu. Kai šis kaištis yra aukštas, prietaisas yra paruoštas perduoti informaciją, jei ne, mikroprocesorius lieka tol, kol šis kaištis pakyla aukštai.

LAIKYKITE

HOLD kaištis nurodo, kada bet kuriame įrenginyje reikalaujama naudoti adresą ir duomenų magistralę. Šie du prietaisai yra LCD ir A / D keitikliai. Tarkime, kad jei A / D keitiklis naudoja adreso magistralę, taip pat duomenų magistralę. Kai LCD nori naudoti abi magistrales teikdamas HOLD signalą, vėliau mikroprocesorius perduoda valdymo signalą link LCD po to, kai bus baigtas esamas ciklas. Kada skystųjų kristalų ekraną procedūra baigta, tada valdymo signalas perduodamas atvirkščiai į A / D keitiklį.

HLDA

Tai yra HOLD atsako signalas ir jis nurodo, ar šis signalas gautas, ar ne. Įgyvendinus HOLD paklausą, šio signalo bus mažai.

IN

Tai yra pertraukimo signalas, kurio prioritetas yra pertraukia yra žemas. Šį signalą gali leisti arba neleisti programinė įranga. Kai INTR kaištis pakyla aukštai, 8085 mikroprocesorius užbaigia vykdomos srovės instrukciją ir tada atpažįsta INTR signalą ir jį vykdo.

INTA

Kai 8085 mikroprocesorius gauna pertraukimo signalą, jis turėtų būti atpažintas. Tai atliks INTA. Dėl to, kai bus pasiektas pertraukimas, INTA padidės.

RST 5,5, RST 6,5, RST 7,5

Šie kaiščiai yra iš naujo paleidžiami pertraukiami arba Vektorizuoti pertraukimai , naudojama pakartotinai įterpiant vidinę restartavimo funkciją. Visi šie pertraukimai yra užmaskuojami, juos galima leisti arba neleisti naudojant programas.

TRAP

Kartu su 8085 mikroprocesoriaus pertraukimais TRAP yra a nemaskuojamas pertraukimas ir tai neleidžia ar sustabdo programa. TRAP turi didžiausią pirmenybę tarp pertraukiklių. Prioritetinė tvarka nuo didžiausios iki mažiausios apima TRAP, RST 5.5, RST 6.5, RST 7.5 ir INTR.

ATSTATYTI

„RESET IN“ kaištis naudojamas programos skaitikliui atstatyti į nulį ir pertvarko pertraukimo įgalinimą, taip pat HLDA šlepetės (FF). Centrinis procesorius yra sulaikomas RST būsena, kol šis kaištis bus aukštas. Tačiau registrai ir vėliavos nebus sugadinti, išskyrus instrukcijų registrą.

RST (RESET) OUT

PIN kodas RESET OUT nurodo, kad centrinis procesorius buvo pertvarkytas naudojant RST IN.

X1 X2

X1, X2 gnybtai, susieti su išoriniu osciliatoriumi, kad būtų sukurtas reikalingas ir tinkamas laikrodžio veikimas.

CLK

Kartais CLK o / PS yra privaloma generuoti iš 8085 mikroprocesorių, kad juos būtų galima naudoti kitų periferinių įrenginių ar kitų skaitmeninių integrinių grandynų naudai. Tai siūloma su CLK kaiščiu. Jo dažnis yra nuolat panašus, nes mikroprocesoriaus veikimo dažnis.

SID

Tai yra nuoseklūs „i / p“ duomenys, o informacija apie šį kaištį įkeliama į 7-ąjį akumuliatoriaus bitą, kol atliekama RIM (skaitymo pertraukimo kaukė) instrukcija. RIM patikrina pertraukimą, ar jis padengtas, ar ne.

SOD

Tai yra nuoseklūs „o / p“ duomenys, o šio kaiščio duomenys siunčia savo išvestį link 7-ojo akumuliatoriaus bitų, kai tik atliekama SIM instrukcija.

VSS ir VCC

VSS yra įžemintas kaištis, o Vcc yra + 5v kaištis. Todėl 8085 kaiščių schema , taip pat signalai yra išsamiai aptariami.

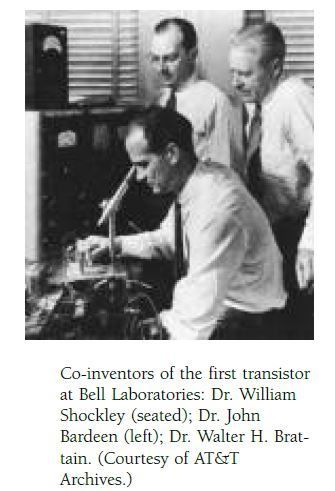

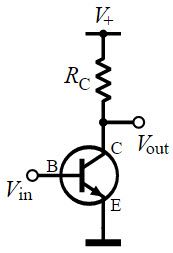

Taigi, viskas apie tai 8085 mikroprocesorius . Pagal aukščiau pateiktą informaciją galime padaryti išvadą, kad tikrasis šio procesoriaus pavadinimas yra 8085A. Šis procesorius yra NMOS įrenginys ir susideda iš tūkstančių tranzistorių. Štai jums klausimas, kokia yra jo funkcija Lygio sukeltas pertraukimas 8085 mikroprocesoriuje?