Terminas VLSI reiškia „labai didelės apimties integravimo technologija“, kuri apima integruotų grandinių (IC) projektavimą, derinant tūkstančius tranzistoriai logiškai į vieną lustą skirtingos logikos grandinės . Šie IC ilgainiui sumažina užimtos grandinės erdvę, palyginti su grandinėmis su įprastais IC. Skaičiavimo galia ir erdvės panaudojimas yra pagrindiniai VLSI dizaino iššūkiai. VLSI projektų įgyvendinimas atveria iššūkių ir ryškią karjerą studentams, taip pat tyrėjams. Kai kurios naujos tendencijos VLSI yra Lauke programuojamas vartų masyvas programų (FPGA), ASIC dizaino ir SOC. Toliau pateikiamas kai kurių VLSI projektų sąrašas tiems studentams, kurie nuoširdžiai siekia projektų šioje srityje. Šiame straipsnyje aptariama VLSI projektų, pagrįstų FPGA, Xilinx, IEEE, Mini, Matlab ir kt., Apžvalga. Šie projektai yra labai naudingi inžinerijos studentams, M.tech studentams.

VLSI projektai inžinerijos studentams

Toliau aptariami VLSI projektai su santraukomis elektronikos inžinerijos studentams.

VLSI projektai

1). Diskrečiosios bangelės transformavimas remiantis 3D kėlimu

Šis projektas padeda pateikti labai tikslius vaizdus, naudojant vaizdo kodavimą, neprarandant jo duomenų. Norėdami tai pasiekti, šiame procese įgyvendinamas kėlimo filtras, priklausomai nuo 3D diskrečios bangos VLSI transformacijos.

2). „SFQ Multiplier“ su 4 bitais efektyviai naudojant didelės spartos aparatinę įrangą projektavimas

Šis projektas daugiausia naudojamas modifikuoto stendo kodavimo įrenginiui (MBE) su 4 bitų SFQ pagrindu įdiegti daugiklis . Šis daugiklis užtikrina gerą našumą, palyginti su įprastu stendo kodavimo įrenginiu. Šis projektas daugiausia naudojamas kritinio uždelsimo programoms.

3). Kriptografijos procesorius, naudojamas intelektualiose kortelėse su efektyviu plotu

Šis projektas naudojamas įgyvendinant tris kriptografijos algoritmus, palaikomus tiek privačių, tiek viešųjų raktų, naudojamų išmanioji kortelė programos, užtikrinančios ypač saugų vartotojo patikrinimą ir duomenis bendravimas .

4). Didelio greičio arba mažos galios daugiklis su netikros galios slopinimo metodu

Siūloma sistema pašalina nenaudingus aritmetinių vienetų melagingus signalus, kad būtų išvengta nereikalingo duomenų perdavimo, kuris neturi įtakos paskutiniams skaičiavimo rezultatams. Ši sistema naudoja SPST metodą daugikliams, kad būtų pasiektas mažos galios ir greitas duomenų perdavimas.

5). Dingusių duomenų algoritmo suspaudimas ir dekompresavimas

Šis projektas daugiausia įgyvendinamas 2 pakopų aparatūros architektūrai, atsižvelgiant į PDLZW (Parallel Dictionary LZW) algoritmo funkciją, taip pat į Adaptive Huffman tipo algoritmą, kuris naudojamas tiek be duomenų praradimo, tiek be nuostolių dekompresijos.

6). Mažo sudėtingumo turbo dekoderio architektūra efektyviai energiją naudojančioms WSN

Siūloma sistema naudojama siekiant sumažinti bendrą energijos suvartojimą perduodant WSN duomenis per skaidantį LUT-Log-BCJR algoritmą į pagrindines ACS (Add Compare Select) operacijas.

7). VLSI architektūra efektyviam vaizdo impulsinio triukšmo pašalinimui

Ši siūloma sistema daugiausia naudojama vizualiai pagerinti vaizdo kokybę, kad būtų išvengta tikimybės sugadinti impulsiniu triukšmu, kad būtų galima įdiegti efektyvią VLSI architektūrą, naudojant kraštus saugantį filtrą.

8). Daugialypės terpės suspaudimui naudojamo atmintyje esančio procesoriaus architektūra

Ši siūloma sistema suteikia nedidelio sudėtingumo architektūrą procesorius atmintyje palaikyti daugialypės terpės programas, būtent vaizdų glaudinimą, vaizdo įrašus taikant milžiniškas vienos instrukcijos, kelių duomenų sąvokas ir instrukcijų žodžius.

9). Laiko sinchronizavimo technika su mažo galingumo belaidžių OFDM sistemų simbolių dažniu

Ši siūloma sistema daugiausia naudojama siekiant pagerinti belaidžio OFDM (ortogonalaus dažnio skyriaus) veikimą Multipleksavimas ) sistemą, laikrodžio pagalba sumažinant visos pagrindinės juostos galią generatorius su fazės derinamu ir dinamišku imties laiko valdikliu.

10). Akumuliatoriaus mažos galios ir didelės spartos daugiklio naudojimas su „SPST Adder & Verilog“

Šis projektas naudojamas suprojektuoti mažos galios ir didelės spartos MAC (daugiklį ir akumuliatorių), priimant klaidingą MBE (modifikuoto kabinų kodavimo įrenginio) galios slopinimo metodą. Naudojant šį dizainą, galima išvengti viso perjungimo galios išsisklaidymo.

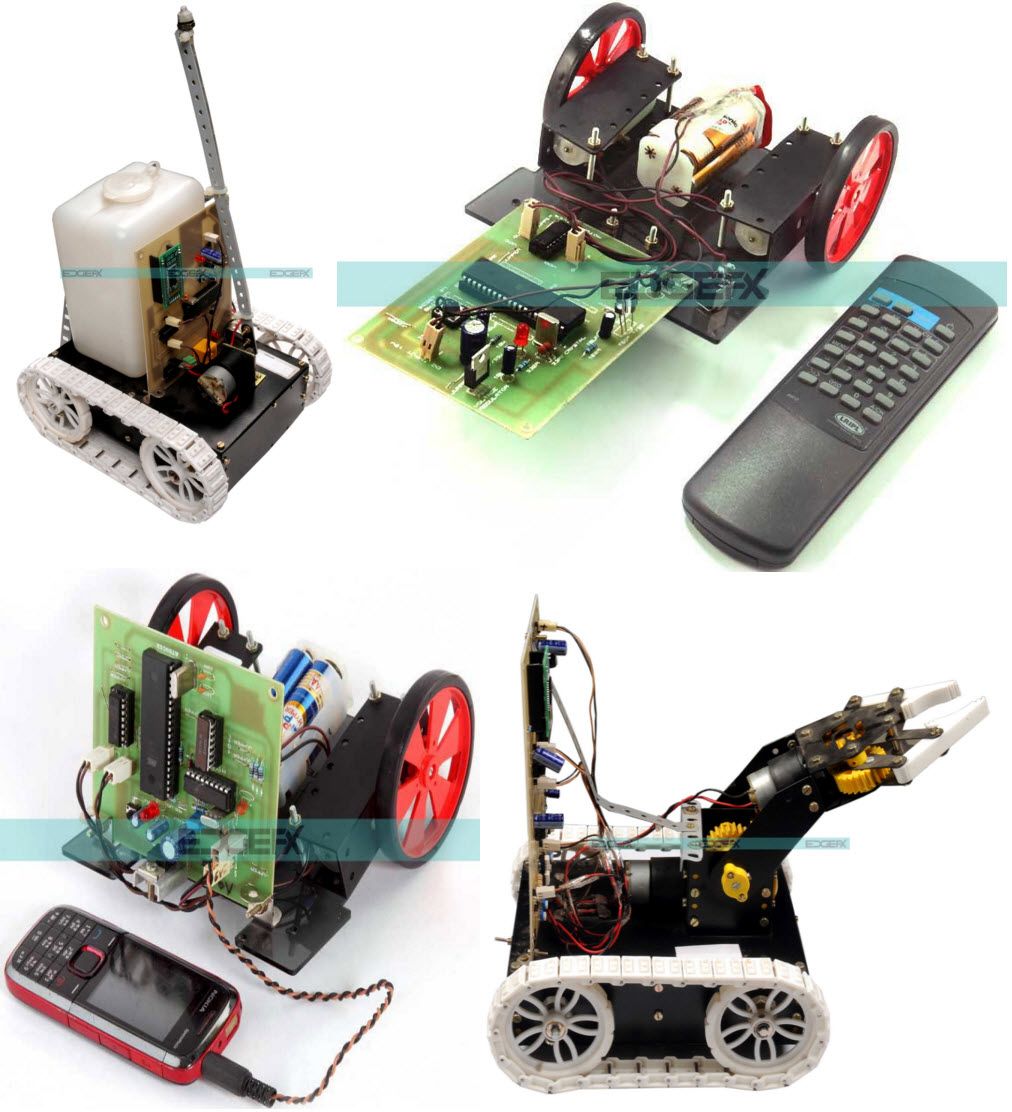

11). Roboto procesoriaus projektavimas ir įgyvendinimas įgalinant apsaugą nuo susidūrimo su RDA technologija

Siūloma sistema daugiausia naudojama robotų procesoriui su anti-susidūrimu įgyvendinti, kad būtų išvengta fizinio robotų susidūrimo kelių robotų aplinkoje. Šis algoritmas daugiausia įgyvendinamas naudojant VHDL ir RFID technologijas.

12). Loginės grandinės su efektyvia energija projektavimas naudojant adiabatinį metodą

Ši sistema demonstruoja loginės grandinės dizainą efektyviai naudojant adiabatinį metodą, palyginti su įprastu CMOS projektu, naudojant grandines, naudojančias NAND & NOR vartai . Taikant adiabatinį metodą, gali būti sumažintas energijos išsklaidymas tinkle, taip pat perdirbama sukaupta energija apkrovos kondensatoriuje.

3). Šifravimo sistema, skirta padidinti sistemos skaičiavimo greitį

Pagrindinė šio projekto nuostata yra pagerinti duomenų perdavimo saugumą ir pagerinti skaičiavimo greitį, įgyvendinant AES algoritmą naudojant FPGA. Taigi, šį modeliavimą, taip pat matematinį dizainą, galima atlikti naudojant VHDL kodą.

14). AHM arba pažangios didelio našumo magistralės IP blokas

Šis projektas daugiausia naudojamas projektuojant „Advanced“ architektūrą Mikrovaldiklis Autobusas (AMB) naudojant AHBN (pažangią didelio našumo magistralę). Šis projektas gali būti sukurtas naudojant VHDL kodą, įgyvendinant tokius blokus kaip „master & save“.

15). DSM pagrįstas daugiareikšmis radijo imtuvas su daugiakanaliu

Ši sistema daugiausia naudojama kuriant daugiamodį siųstuvo ir imtuvo architektūrą bei RF daugiakanalį moduliavimą su „Delta-Sigma“. Ši siūloma sistema naudoja VHDL kalbą dviem architektūroms įgyvendinti.

16). Išjungimo koncentratorius naudojant asinchroninį perdavimo režimą

Naudojant šį projektą, asinchroniniu perdavimu pagrįstas išjungimo jungiklis gali būti sukurtas naudojant tokius įrankius kaip VHS ir VHDL. Šis išjungimo jungiklis gali būti naudojamas virtualių grandinių paketų tinkluose, taip pat datagramos programose.

17). Asinchroninių grandinių elgesio sintezė

Šis projektas daugiausia naudojamas siekiant pateikti elgesio sintezės metodiką, naudojamą asinchroninėms grandinėms. Abu šablonai, tokie kaip „balsa“ ir asinchroniniai diegimai, yra pagrindiniai dizaino elementai.

18). AMBA dizainas naudojant suderinamą AHB atminties valdiklį

Šis projektas naudojamas kuriant MC (atminties valdiklį), priklausomai nuo AMBA (išplėstinės mikrovaldiklio magistralės architektūros) sistemos atminties valdymui naudojant pagrindinę atmintį, pvz., SRAM ir ROM.

19). „Carry Tree Adder“ įgyvendinimas

Remiantis VLSI dizainu, nešiojimo medžio sumedžiotojai yra vadinami geriausiais našumo sumetėjais, palyginti su įprastais dvejetainiais priedais. Pagal šį projektą įgyvendinami pridėtiniai medžiai, kogge akmuo ir retas kogge akmuo.

20). „CORDIC“ dizainu pagrįstas fiksuoto kampo sukimas

Pagrindinė šios siūlomos sistemos koncepcija yra vektorių pasukimas naudojant fiksuotus kampus. Šie kampai reikalingi žaidimams, robotikai, vaizdo apdorojimas ir kt. Naudojant šį projektą, vektoriaus sukimąsi galima pasiekti naudojant specialius kampus pagal CORDIC (koordinačių sukimosi skaitmeninis kompiuteris) projektą.

21). FIR filtro dizainas su paskirstyta paieškos lentelės aritmetika

Ši siūloma sistema daugiausia patobulina FIR filtras našumas suprojektuojant jį naudojant daugiamatės paskirstytą 3 dimensijų paieškos lentelės aritmetiką. Taigi šį dizainą galima įgyvendinti naudojant tokias programines priemones kaip FPGA ir Xilinx.

22). Push-Pull impulsiniai skląsčiai su dideliu greičiu ir mažos galios sąlyginiais

Šis projektas naudojamas energiją taupantiems ir didelio našumo impulsiniams skląsčiams, dažniausiai naudojamiems VLSI sistemoms, panaudoti naudojant naują topologiją. Kadangi ši topologija daugiausia priklauso nuo paskutinio etapo stūmimo traukos, važiuojančio dviem padalijimo juostomis per sąlyginį impulsų generatorių.

23). Aritmetinis koderis VLSI architektūra SPIHT

Ši siūloma sistema padidina aritmetinio kodavimo metodo našumą nustatant skaidymą hierarchinių medžių (SPIHT) vaizdų glaudinimo srityje, naudojant didelės spartos architektūrą, priklausomai nuo FPGA.

24). EKP signalo slopinimas pagal FPGA

Šis projektas naudojamas triukšmui sulaikyti per EKG signalus per du vidutinius filtrus, kurių imties taškų dydis yra atitinkamai 91 ir 7. Taigi šį procesą galima pasiekti įgyvendinant FPGA dizainas remiantis VHDL kodu.

25). VLSI pagrįstas didelio našumo vaizdo keitimo procesorius su mažomis sąnaudomis

Šis projektas naudojamas įgyvendinti vaizdo mastelio procesoriaus, pagrįsto VLSI, algoritmą, turintį mažiau atminties ir aukštą našumą. Siūlomoje sistemos konstrukcijoje daugiausia yra filtrų, perkonfigūruojamų dinaminių metodų ir aparatinės įrangos naudojimo derinimas, siekiant sumažinti išlaidas.

26). Efektyvus sistolinio matricos architektūros projektavimas ir įgyvendinimas

Pagrindinė šio projekto koncepcija yra aparatinės įrangos modelio, naudojamo sistolinio masyvo daugikliui, sukūrimas. Ši masyvas daugiausia gali būti naudojamas vykdant dvejetainį dauginimą VHDL platformos pagalba. Siūlomas sistemos dizainas gali būti įgyvendinamas naudojant FPGA & Isim programinę įrangą.

27). QPSK dizainas ir sintezė naudojant VHDL kodą

QPSK yra vienas iš pagrindinių moduliacijos metodų. Šis metodas naudojamas taikant palydovinį radiją. Ši moduliavimo technika gali būti įgyvendinta per grįžtamuosius loginius vartus. Projektuoti QPSK techniką galima naudojant VHDL kodą.

28). DDR SDRAM valdiklio projektavimas ir įgyvendinimas dideliu greičiu

Siūloma sistema naudojama DDR SDRAM valdikliui suprojektuoti, kad būtų galima perduoti serijos duomenis, priklausomai nuo didelio greičio, kad šie duomenys būtų sinchronizuojami tarp įterptosios sistemos ir DDR SDRAM schemų. Naudojant VHDL kalbą, kodą galima sukurti.

29). 32 bitų RISC procesoriaus projektavimas ir įgyvendinimas

Pagrindinė šio projekto koncepcija yra 32 bitų diegimas RISC (sumažintas instrukcijų rinkinys) naudojant tokį įrankį kaip XILINK VIRTEX4. Šiame projekte yra sukurta 16 komandų rinkinių visur, kur kiekvieną komandą galima įvykdyti per vieną CLK ciklą naudojant penkių fazių vamzdynų metodą.

30). „Bus Bridge“ diegimas tarp AHB ir OCP

Siūloma sistema naudojama projektuojant magistralinį tiltą tarp dviejų protokolų, būtent bendro ir standartinio. Ryšio protokolai, tokie kaip AHB (išplėstinė didelio našumo magistralė) ir OCP (atvirojo branduolio protokolas), yra labai populiarūs, kurie naudojami SoC (lustinė sistema) .

VLSI projektų idėjos inžinerijos studentams

Žemiau pateiktas VLSI projektų, pagrįstų FPGA, MatLab, IEEE ir Mini projektais, inžinerijos studentams sąrašas.

VLSI projektai M. technikos studentams

VLSI projektų, paremtų M. Tech studentais, sąraše yra šie.

- Erdvus ir labai patikimas RHBD pagrįstas I0T atminties elementų dizainas, naudojamas aviacijos ir kosmoso programose

- Fazės detektorius su daugiapakopiu pusės greičiu, naudojamas CLK ir duomenų atkūrimo grandinėms

- Lyginamasis su mažos galios ir dideliu greičiu, naudojamas tikslioms programoms

- Vartinis įtampos lygio vertėjas su didelio našumo ir integruotu multiplekseriu

- CNTFET pagrįstas „Ternary Adder“ su didelio našumo

- Dydžio palyginimo dizainas su maža galia

- Slenkstinių loginių vartų su srovės režimu projektavimas vėlavimo analizei

- Mišraus logikos linijų dekoderių dizainas su mažos galios ir našumu

- Miego konvencijos logikos testavimo dizainas

- Įtampos lygio perjungiklis dvigubo maitinimo programoms, naudojančioms didelę spartą ir energiją

- Mažos galios ir žemos įtampos dvigubo uodegos komparatoriaus dizainas ir analizė

- „Flip-Flop“ dizainas, pagrįstas impulso suveikimu su maža galia, naudojant signalo perdavimo metodą

- Efektyvus grandinių dizainas, pagrįstas vykdymo laiko pertvarkomais FET

- Dydžio palyginimo dizainas su maža galia

- Vėluojama analizuoti loginių vartų dizainus su dabartinio režimo slenksčiu

FPGA paremti VLSI projektai inžinerijos studentams ir CMOS VLSI projektavimo mini projektai yra išvardyti toliau.

- SEU grūdintų grandinių projektavimas ir apibūdinimas FPGA, pagrįstas SRAM

- Kompaktiškas „Memristor“ pagrindu sukurtas CMOS hibridinis LUT dizainas ir potenciali programa, naudojama FPGA

- Ultragarso jutikliu pagrįstas FPGA įgyvendinimas atstumui matuoti

- FPGA diegimas stendo daugikliui su Spartan6 FPGA

- Diskreti „Wavelet“ transformacija, pagrįsta kėlimu su „Spartan3 FPGA“

- ARM valdiklis robotikoje, naudojant FPGA

- FPGA pagrindu sukurta UART su daugiakanaliu

- EKG signalo triukšmo slopinimas naudojant FPGA

- UTMI pagrįstas FPGA diegimas ir USB 2.0 protokolo sluoksnis

- Vidutinio filtro diegimas naudojant „Spartan3 FPGA“

- AES algoritmu pagrįstas FPGA įgyvendinimas

- Saugos perspėjimo sistema, pagrįsta PIC, skirta FPGA diegimui su „Spartan 3an“

- FPGA diegimas valdant nuotolinio aptikimo sistemas

- FPGA vaizdo apdorojimo rinkinys, naudojant linijinio ir morfologinio vaizdo filtravimą

- „Spartan3 FPGA“ pagrindu sukurtas medicininio sintezės vaizdo įgyvendinimas

Sąrašas VLSI mini projektai, naudojant VHDL kodą apima šiuos dalykus.

- Palyginamas su dideliu greičiu naudojant VLSI

- Plūduriuojančio taško daugiklis naudojant VLSI

- VLSI pagrįstas dvejetainio pavertimas pilka

- Skaitmeninis filtras

- CLK vartai pagal VLSI

- Vedų daugiklis

- CMOS FF naudojant VLSI

- Lygiagretaus procesoriaus, naudojančio VLSI, architektūra

- VLSI „Full Adder“

- DRAM / dinaminės laisvosios kreipties atminties, pagrįstos VLSI, projektavimas

- SRAM maketas pagal VLSI

- VLSI pagrįstas skaitmeninio signalo procesorius

- VLSI pagrindu sukurtas multiplekseris

- MAC bloko projektavimas remiantis VLSI

- VLSI pagrįstas diferenciatorius

- VLSI pagrįstas FFT arba greitas Furjė transformavimas

- Diskrečiojo kosinuso transformacijos, pagrįstos VLSI, architektūra

- 16 bitų daugiklio dizainas naudojant VLSI19

- VLSI pagrįstas FIFO buferio projektavimas

- Didelio greičio greitintuvas, pagrįstas VLSI

VLSI projektai naudojant MATLAB ir Xilinx

VLSI projektų, pagrįstų MATLAB ir VLSI projektais, naudojančiais „Xilinx“, sąrašą yra šie.

- CDMA modemo projektavimas ir analizė naudojant MATLAB

- FIR filtro dizainas naudojant VHDL FPGA ir MATLAB pagrindu

- „ModelSim & Matlab“ arba „Simulink“ pagrindu sukurta automobilių inžinerijos sistemos modeliavimas

- „Xilinx“ pagrindu pagaminti priedai, tokie kaip „Ripple Carry & Carry Skip“

- Aritmetinis vienetas, pagrįstas 32 bitų slankiuoju tašku

- Plūduriuojančio taško ALU

- RISC procesorius pagrįstas 32 bitų

- Stačiakampio kodo konversijos galimybės

- „Xilinx“ ir „Verilog“ automatai

- „Xilinx“ pagrindu sukurti lygiagrečių prefiksų priedai su 256 bitais

- Abipusio autentifikavimo naudojant „Xilinx“ protokolas

- Prieiga prie vieno ciklo loginio bandymo naudojant „Xilinx“ struktūrą

- UTMI ir protokolo sluoksnis pagrįstas USB2.0, naudojant „Xilinx“

- Duomenų glaudinimo ir dekompresavimo konfigūravimas naudojant Xilinx FPGA

- „Xilinx 4000“ pagrindu pagaminti BIST ir „Spartan“ serijos FPGA

- IIR filtras pagrįstas MATLAB ir VLSI

- FIR filtras naudojant MATLAB

IEEE projektai

IEEE VLSI projektų sąrašas yra išvardytas žemiau.

- VLSI pagrįsta belaidė namų automatikos sistema, naudojanti „Bluetooth“

- Impulsinio triukšmo pašalinimas paveikslėlyje naudojant efektyvią VLSI architektūrą

- Daugialypės terpės suspaudimo procesoriaus atmintyje architektūra

- Temperatūros sistemos stebėjimas naudojant „Cloud & IoT“

- OFDM sistemos diegimas naudojant IFFT & FFT

- Hammingo kodo projektavimas ir įgyvendinimas naudojant „Verilog“

- VHDL pirštų atspaudų atpažinimas naudojant „Gabor“ filtrą

- Aritmetinių funkcijų pakeitimas naudojant ROM, atsižvelgiant į aproksimavimo metodus

- Didelio efektyvumo ir mažo tankio pariteto tikrinimo kodo dekoderio našumo analizė mažos galios programose

- „FFT“ architektūros su grįžtamuoju ryšiu iš vamzdynų „Radix-2k“

- „Flip-Flops“ dizainas VLSI programoms, naudojant didelio našumo CMOS technologiją

- FIR filtro dizainas su paieškos lentele pagal paskirstytą aritmetiką

- VLSI pagrįstas nebrangus ir patobulintas vaizdo mastelio procesorius

- ASIC išankstinio turbokoderio ir dekoderio su 3GPP LTE diegimas ir dizainas

- „Push-Pull“ impulsiniai skląsčiai su mažos galios ir dideliu greičiu

- Patobulintas nuskaitymas atliekant mažos galios nuskaitymo testavimą

- Aritmetinis koderis VLSI SPIHT architektūra

- UHD VHDL diegimas

- VLSI pagrįstas įtampos reguliatorius su mažu iškritimu

- „Flash ADC Design“ su patobulinta komparatoriaus schema

- Mažos galios daugiklio dizainas su junginio pastovaus vėlavimo loginiu stiliumi

- Dvigubas uodegos lygintuvas su didelio našumo ir mažos galios

- „Flash“ laikymo sistema su dideliu našumu, priklausomai nuo įrašymo buferio ir virtualiosios atminties

- Mažos galios FF, pagrįstas mieguisto kamino metodu

- LFSR energijos optimizavimas mažos galios BIST, įdiegtas HDL

- Prekybos automatų projektavimas ir įgyvendinimas naudojant „Verilog HDL“

- Akumuliatoriaus dizainas, pagrįstas 3 svorio modelio su LP-LSFR generavimu

- „Reed-Solomon“ dekoderis su dideliu greičiu ir mažu kompleksiškumu

- Greitesnė „Dadda“ daugiklio projektavimo technika

- Skaitmeninis demoduliacinis FM radijo imtuvas

- Testo modelio su BIST schemomis generavimas

- VLSI architektūros su greitųjų vamzdynų įgyvendinimas

- „On-Chip Bus“ OCP protokolo projektavimas naudojant magistralės funkcijas

- Fazių dažnio detektorius ir įkrovimo siurblio dizainas, naudojamas aukšto dažnio fazėje užrakintoje kilpoje

- Talpyklos atminties ir talpyklos valdiklio dizainas su VHDL

- ASTRAN pagrįstas mažos galios 3-2 ir 4-2 papildiklių kompresorių įgyvendinimas

- Išankstinio apmokėjimo už elektros energiją sistema, naudojant „On-Chip“ dizainą

- Persidengimas naudojant loginį langelį ir jo galios analizę

- „Carry Look Ahead Adder“ naudojant skirtingą bitų našumo analizę naudojant VHDL

- Duomenų ryšio sluoksnio dizainas naudojant „Wi-Fi MAC“ Protokolai

- FPGA įgyvendinimas abipusio autentifikavimo protokolui su moduline aritmetika

- PWM signalo generavimas naudojant FPGA ir kintamą darbo ciklą

Realaus laiko projektai

Sąrašas VLSI realaus laiko projektai daugiausia apima VLSI mini projektus, naudojančius VHDL kodą, ir VLSI programinės įrangos projektus ECE inžinerijos studentams.

- Pragmatiškas SRAM eilučių talpyklos integravimas heterogeniškoje 3-D DRAM architektūroje naudojant TSV

- Integruota savikontrolės technika vėluojančių gedimų diagnostikai grupių pagrindu programuojamuose vartų matricose

- ASIC kompleksinio daugiklio projektavimas

- Pigus VLSI diegimas efektyviam impulsinio triukšmo pašalinimui

- FPGA pagrindu Erdvės vektoriaus PWM Trifazio asinchroninio variklio valdymo IC

- VLSI automatinio koreliatoriaus ir CORDIC algoritmo diegimas OFDM pagrįstam WLAN

- Automatinis kelio ištraukimas naudojant aukštos raiškos palydovinius vaizdus

- VHDL dizainas vaizdų segmentavimui naudojant Gaboro filtrą ligoms nustatyti

- Mažo sudėtingumo turbo dekoderio architektūra efektyviai energiją naudojantiems belaidžių jutiklių tinklams

- Stačiakampio kodo konversijos galimybių tobulinimas naudojant FPGA diegimą

- Plūduriuojančio taško ALU projektavimas ir įgyvendinimas

- CORDIC fiksuoto pasukimo kampo dizainas

- Produkto „Reed-Salomon“ kodai, skirti įdiegti NAND „Flash“ valdiklį FPGA lustui

- Statistinis SRAM skaitymo prieinamumo gerinimas naudojant neigiamos talpos grandines

- MIMO tinklo sąsajų galios valdymas mobiliosiose sistemose

- Duomenų šifravimo duomenų šifravimo standarto projektavimas

- Mažos galios ir ploto efektyvus nešiojimo pasirinkimas

- UART sintezė ir diegimas naudojant VHDL kodus

- Patobulintos sulydyto plūduriuojančio taško sudedamųjų ir atimamųjų dalių architektūros

- FPGA pagrindu sukurtas 1 bitų skaitmeninis siųstuvas, kuriame naudojama „Delta-Sigma“ moduliacija su RF išvestimi SDR

- Tinklo paieškos optimizavimas BCH dekoderyje, kad būtų perduotas didelis klaidų lygis

- Skaitmeninis DS-CDMA siųstuvo dizainas naudojant „Verilog HDL“ ir „FPGA“

- Efektyvios sistolinės masyvo architektūros projektavimas ir įgyvendinimas

- VLSI pagrįstas robotų dinamikos mokymosi algoritmas

- Universalus daugialypės terpės funkcinių įrenginių dizainas, naudojant netikrą energijos slopinimo techniką

- Autobusų tilto tarp AHB ir OCP projektavimas

- Asinchroninių grandinių elgesio sintezė

- FPGA modifikuoto „Viterbi“ dekoderio greičio optimizavimas

- I2C sąsajos įgyvendinimas

- Didelio greičio / mažos galios daugiklis, naudojant pažangią klastingos galios slopinimo techniką

- Viršutinio maitinimo grandinių virtualios maitinimo įtampos užspaudimas aktyviam nuotėkio mažinimui ir vartų oksido patikimumui

- FPGA pagrįstas efektyviai valdomas kanalizatorius programinės įrangos radijui

- Skaitmeninio fotoaparato VLSI architektūra ir FPGA prototipai, skirti vaizdo apsaugai ir autentifikavimui

- Roboto patalpose tobulinimas

- Daugiaprocesorinės sistemos „On-Chip“ ON-Chip permatacijos tinklo projektavimas ir įgyvendinimas

- Mažos galios belaidžių OFDM sistemų simbolių greičio sinchronizavimo metodas

- DMA valdiklis (tiesioginė prieiga prie atminties), naudojant VHDL / VLSI

- Pertvarkomas FFT, naudojant CORDIC pagrįstą architektūrą MIMI-OFDM imtuvams

- Neįtikėtina daugialypės terpės / DSP programų maitinimo mažinimo technika

- BCH kodų efektyvumas skaitmeninio vaizdo vandenženklyje

- Dvigubo duomenų perdavimo greičio SD-RAM valdiklis

- „Gabor“ filtro diegimas pirštų atspaudams atpažinti naudojant „Verilog HDL“

- Praktiškos nanometro skalės perteklinis dizainas per „Aware Standard“ ląstelių biblioteką, kad būtų patobulinta nereikalinga per 1 įterpimo greitį

- Dingusių duomenų suspaudimo ir dekompresijos algoritmas ir jo aparatinės įrangos architektūra

- Daugybinių minkštųjų klaidų taisymo sistema

- „Viterbi“ pagrindu sukurtas efektyvus bandymo duomenų suspaudimas

- OFDM FFT / IFFT blokų diegimas

- Vaizdo glaudinimas bangomis pagrįstas progresyviu VLSI kodavimu

- VLSI „Full Pipelined Multiplier Less 2d DCT / IDCT Architecture for JPEG“ įgyvendinimas

- FPGA pagrįstas sinchroninių nuosekliųjų grandinių gedimų imitavimas

Taigi, viskas susiję su VLSI inžinerijos projektų, M.Tech studentų, kurie yra naudingi parenkant paskutinių metų projekto temą, sąrašu. Praleidę brangų laiką, peržiūrėdami šį sąrašą, manome, kad turite gana gerą idėją pasirinkti savo pasirinktą projekto temą iš VLSI projektų sąrašo ir tikimės, kad turėsite pakankamai pasitikėjimo, kad galėtumėte perimti bet kurią temą iš sąrašą. Norėdami gauti daugiau informacijos ir pagalbos įgyvendinant šiuos projektus, galite parašyti mums toliau pateiktame komentarų skyriuje. Štai jums klausimas, kas yra VHDL?

Nuotraukų kreditas

- VLSI projektai set-tech