Per pastaruosius kelerius metus skaitmeninės aparatūros projektavimo procesas intensyviai keitėsi. Taigi, mažos skaitmeninės grandinės gali būti įdiegtos naudojant PAL ir PLA. Kiekvienas prietaisas yra naudojamas įgyvendinti įvairias grandines kuriems nereikia daugiau nei konkrečiame luste siūlomų i / ps, o / ps ir produktų terminų. Šie lustai yra netinkami gana kukliems dydžiams, paprastai palaikantys abiejų įėjimų ir išėjimų skaičių, ne didesnį kaip 32. Norint suprojektuoti šias grandines, kurioms reikia daugiau įėjimų ir išėjimų, galima naudoti daugybę PLA / PAL, arba klasikinio tipo lusto gali būti naudojamas vadinamas CPLD (sudėtingas programuojamas loginis įrenginys). CPLD lustą sudaro keli grandinės blokai vienoje mikroschemoje su vidiniais laidų šaltiniais grandinių blokams pritvirtinti. Kiekvienas grandinės blokas yra palyginamas su PLA arba PAL.

Kas yra sudėtingas programuojamas loginis įrenginys?

CPLD santrumpa yra „Sudėtingi programuojami loginiai įrenginiai“, tai yra vienas integruoto grandyno rūšis kad programų dizaineriai suprojektuotų įdiegti skaitmeninę techninę įrangą, pavyzdžiui, mobiliuosius telefonus. Jie gali valdyti žinomai aukštesnį dizainą nei SPLD (paprasti programuojami loginiai įrenginiai), tačiau siūlo mažiau logikos nei FPGA ( lauko programuojami vartų matricos ). CPLD yra daugybė loginių blokų, kiekviename iš jų yra 8–16 makrokelio. Kadangi kiekvienas loginis blokas vykdo tam tikrą funkciją, visos loginio bloko makrocelės yra visiškai sujungtos. Priklausomai nuo naudojimo, šie blokai gali būti tarpusavyje sujungti arba ne.

Kompleksinis programuojamas loginis įrenginys

Daugumoje CPLD (sudėtingų programuojamų loginių įrenginių) yra makrocelės su loginės funkcijos ir pasirenkamosios sumos suma FF (šlepetė) . Priklausomai nuo mikroschemos, kombinatorinė logikos funkcija palaiko nuo 4 iki 16 produkto sąlygų su įtraukiamu ventiliatoriumi. CPLD taip pat skiriasi pagal pamainų registrus ir loginius vartus. Dėl šios priežasties vietoj FPGA gali būti naudojami CPLD su dideliu loginių vartų skaičiumi. Kita CPLD specifikacija nurodo produktų terminų, kuriuos gali atlikti makrocelė, skaičių. Produkto terminai yra skaitmeninių signalų, vykdančių tam tikrą loginę funkciją, produktas.

CPLD yra keliose IC paketų formose ir logikos šeimose. CPLD taip pat skiriasi maitinimo įtampa, darbine srove, budėjimo srove ir energijos išsklaidymu. Be to, juos galima gauti su įvairiais atminties kiekiais ir įvairių rūšių atmintimi. Paprastai atmintis išreiškiama bitais / megabitais. Atminties palaikymas susideda iš ROM, RAM ir dviejų prievadų RAM. Jį taip pat sudaro CAM (turinio adresinė atmintis), taip pat FIFO („first-in, first-out“) atmintis ir LIFO („last-in, last-out“) atmintis.

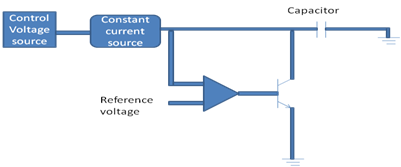

Kompleksinio programuojamo loginio įrenginio architektūra

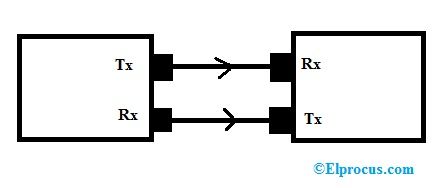

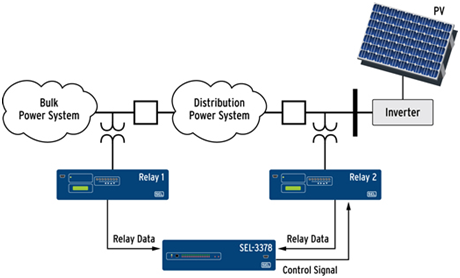

Kompleksinį programuojamą loginį įtaisą sudaro programuojamų FB (funkcinių blokų) grupė. Šių funkcinių blokų įėjimai ir išėjimai yra sujungti GIM (visuotinio sujungimo matrica). Ši sujungimo matrica yra pertvarkoma, kad galėtume modifikuoti kontaktus tarp funkcinių blokų. Bus keletas įvesties ir išvesties blokų, kurie leis mums sujungti CPLD su išoriniu pasauliu. CPLD architektūra parodyta žemiau.

Paprastai programuojamas FB atrodo kaip loginių vartų masyvas , kur galima užprogramuoti AND vartų masyvą, o ARBA vartai yra stabilūs. Bet kiekvienas gamintojas turi savo mąstymo būdą suprojektuoti funkcinį bloką. Išvardytą o / p galima rasti veikiant grįžtamojo ryšio signalams, pasiekiamiems iš OR vartų išėjimų.

CPLD architektūra

Programuojant CPLD, dizainas pirmiausia užkoduojamas „Verilog“ arba „VHDL“ kalba, kai kodas yra (imituojamas ir susintetinamas. Sintezės metu pasirenkamas CPLD modelis (tikslinis įrenginys) ir sudaromas technologijomis pagrįstas žemėlapių tinklo sąrašas. Šis sąrašas gali būti arti - pritaikyti tikrą CPLD architektūrą, naudojant vietos ir maršruto procesą, paprastai pasiekiamą naudojant „CPLD Company“ nuosavybės programinę įrangą. Tada operatorius atliks patvirtinimo procesus. Jei viskas gerai, jis naudos CPLD, dar kitaip jis tai pertvarkys.

CPLD architektūros klausimai

Svarstant sudėtingą programuojamą loginį įrenginį, skirtą naudoti projektuojant, galima atsižvelgti į keletą šių architektūros problemų

- Programavimo technologija

- Funkcijų blokavimo galimybė

- Įvesties / išvesties galimybė

Įtraukiamos kai kurios CPLD šeimos iš skirtingų mažmenininkų

- „Altera MAX 7000“ ir „MAX 9000“ šeimos

- ATMEL ir ATV šeimos

- Lattice isp LSI šeima

- Grotelių (Vantis) MACH šeima

- „Xilinx XC9500“ šeima

CPLD šeimos

CPLD programos

CPLD taikymo sritis yra šios

- Kompleksiniai programuojami loginiai prietaisai idealiai tinka didelio našumo, kritinio valdymo programoms.

- CPLD gali būti naudojamas skaitmeniniuose projektuose, norint atlikti įkrovos funkcijas

- CPLD naudojamas lauko programuojamų vartų masyvo konfigūracijos duomenims krauti iš nepastovios atminties.

- Paprastai jie naudojami mažose dizaino programose, tokiose kaip adresų dekodavimas

- CPLD dažnai naudojami daugelyje programų, pvz., Nešiojamiems nešiojamiems prietaisams, susijusiems su sąnaudomis, dėl mažo dydžio ir mažo energijos vartojimo.

Taigi, viskas yra apie sudėtingą programuojamą loginio įrenginio architektūrą ir jos programas. Tikimės, kad jūs geriau supratote šią koncepciją. Be to, bet kokie klausimai dėl šios koncepcijos ar įgyvendinti bet kokius elektrinius ir elektroninius projektus , pateikite savo vertingus pasiūlymus komentuodami žemiau esančiame komentarų skyriuje. Čia jums kyla klausimas, kuo skiriasi CPLD ir FPGA?

Nuotraukų kreditai:

- CPLD wikimedia

- CPLD architektūra slidesharecdn