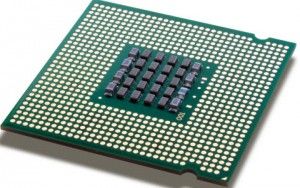

ATmega32 - 8 bitų AVR mikrovaldiklis

AVR mikrovaldikliai yra pagrįsti pažangia RISC architektūra. „ATmega32“ yra mažos galios CMOS 8 bitų mikrovaldiklis, pagrįstas AVR patobulinta RISC architektūra. AVR gali įvykdyti 1 milijoną nurodymų per sekundę, jei ciklo dažnis yra 1 MHz.

40 kontaktų DIP „ATmega32“ nuotrauka

Pagrindiniai bruožai:

- 32 x 8 bendrosios paskirties registrai.

- 32 tūkst. Baitų sistemos programuojamoje „Flash“ programos atmintyje

- 2K vidinio SRAM baitų

- 1024 baitai EEPROM

- Yra 40 kontaktų DIP, 44 laidų QTFP, 44 padų QFN / MLF

- 32 programuojamos įvesties / išvesties linijos

- 8 kanalai, 10 bitų ADC

- Du 8 bitų laikmačiai / skaitikliai su atskirais preskaleriais ir palygina režimus

- Vienas 16 bitų laikmatis / skaitiklis su atskiru preskaleriu, palyginkite režimą ir fiksavimo režimą.

- 4 PWM kanalai

- Sistemos programavime pagal lusto įkrovos programą

- Programuojamas budėjimo šuns laikmatis su atskiru lusto osciliatoriumi.

- Programuojamas serijinis USART

- Šeimininko / vergo SPI nuoseklioji sąsaja

Specialios mikrovaldiklio savybės:

- Šeši miego režimai: tuščiosios eigos, ADC triukšmo mažinimas, energijos taupymas, išjungimas, budėjimo režimas ir išplėstinis budėjimo režimas.

- Vidinis kalibruotas RC osciliatorius

- Išoriniai ir vidiniai pertraukimo šaltiniai

- Įjunkite atstatymą ir programuojamą rudos spalvos aptikimą.

40 kontaktų „ATmega32“ DIP

Visi 32 registrai yra tiesiogiai prijungti prie aritmetinės logikos bloko (ALU), leidžiančio pasiekti du nepriklausomus registrus vienu nurodymu, vykdomu per vieną laikrodžio ciklą.

Išjungus maitinimą, išsaugomas registro turinys, bet užšaldomas osciliatorius. Visos kitos lusto funkcijos bus išjungtos iki kito išorinio pertraukimo. Asinchroninis laikmatis leidžia vartotojui palaikyti laikmatį, veikiantį energijos taupymo režimu, kai likusi prietaiso dalis miega.

ADC triukšmo mažinimo režimas sustabdo procesorių ir visus įvesties / išvesties modulius, išskyrus ADC ir asinchroninį laikmatį. Budėjimo režimu, išskyrus kristalinį osciliatorių, likęs prietaisas miega. Ir pagrindinis osciliatorius, ir asinchroninis laikmatis toliau veikia prailgintu budėjimo režimu.

„ATmega32“ yra galingas mikrovaldiklis, nes monolitiniame luste sistemoje yra savaime programuojama blykstė. Tai yra labai lankstus ir ekonomiškas sprendimas daugeliui įterptųjų valdymo programų.

44 padų TQFP / MLF

Smeigtukų aprašymai:

VCC: Skaitmeninis įtampos tiekimas

BND: Žemė

A jungtis (PA7-PA0): Šis prievadas naudojamas kaip analoginiai įėjimai į A / D keitiklį. Jis taip pat naudojamas kaip 8 bitų dvikryptis įvesties / išvesties prievadas, jei nenaudojamas A / D keitiklis.

B prievadas (PB7-PB0) ir D prievadas (PD7-PD0): Tai yra 8 bitų dvikryptis įvesties / išvesties prievadas. Jo išvesties buferiai turi simetriškas pavaros charakteristikas, pasižyminčias dideliu kriaukle ir šaltiniu. Kaip įėjimai, jie yra labai žemai, jei įjungiami traukimo rezistoriai. Jis taip pat tarnauja įvairioms „ATmega32“ funkcijoms.

C prievadas (PC7-PC0): Tai yra 8 bitų dvikryptis įvesties / išvesties prievadas. Jei įjungta JTAG sąsaja, suaktyvinami rezistoriai ant kaiščių PC5 (TDI), PC3 (TMS) ir PC2 (TCK).

JTAG sąsaja naudojant ATmega32 C prievadą

Nustatyti iš naujo: Tai yra indėlis.

XTAL1: Tai įvestis į invertuotojo osciliatoriaus stiprintuvą ir įvestis į vidinio laikrodžio veikimo grandinę.

XTAL2: Tai yra invertuotojo osciliatoriaus stiprintuvo išvestis.

AVCC: Tai yra A ir A / D keitiklių maitinimo įtampos kaištis. Jis turėtų būti prijungtas prie VCC.

AREF: AREF yra analoginis A / D keitiklio atskaitos kaištis.

„ATmega32“ prisiminimai:

Jame yra dvi pagrindinės atminties vietos duomenų ir programos atminties vietos. Be to, jame yra EEPROM atmintis, skirta duomenims saugoti.

Sistemoje programuojamoje „Flash“ programos atmintyje:

„ATmega32“ sistemoje perprogramuojama „Flash“ atmintis, turinti 32 MB, lustą, skirtą programoms laikyti. „Flash“ yra organizuojamas kaip 16k X 16, o jo atmintis yra padalinta į dvi dalis: „Boot“ programos programa ir programos programa.

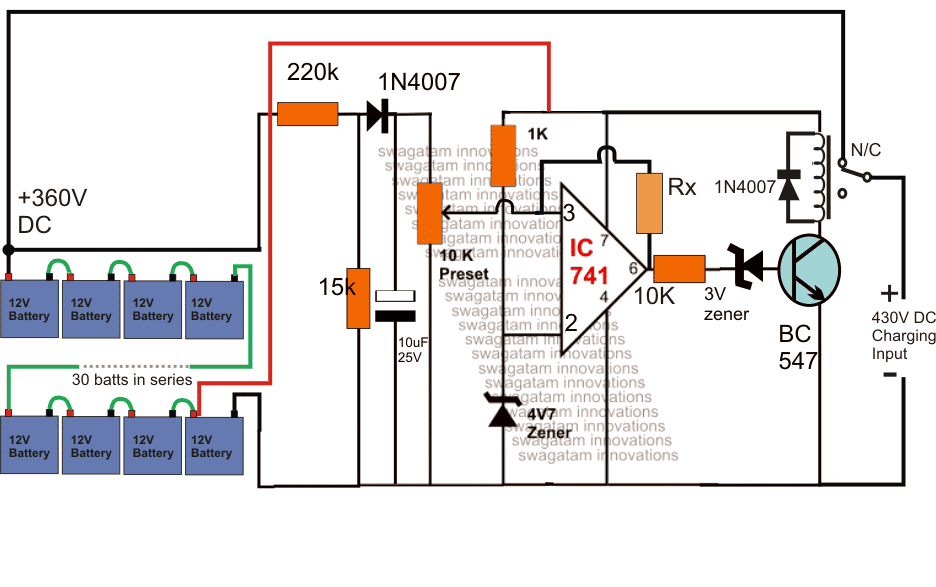

ISP programuotojo grandinės schema

SRAM duomenų atmintis:

„Register“ failą, įvesties / išvesties atmintį ir vidinius duomenis SRAM adresuoja apatinės 2144 duomenų atminties vietos. Pirmosios 96 vietos adresuoja registro failą ir įvesties / išvesties atmintį, o vidinius duomenis SRAM adresuoja kitos 2048 vietos. Tiesioginiai, netiesioginiai su poslinkiu, netiesioginiai, netiesioginiai - prieš sumažinimą ir tiesioginiai - po sumažinimo yra 5 skirtingi duomenų atminties adresavimo režimai. 32 bendrosios paskirties registrai, 64 įvesties / išvesties registrai ir 2048 baitai vidinių duomenų SRAM yra pasiekiami naudojant šiuos adresavimo režimus.

ATmega32 blokinė schema

EEPROM duomenų atmintis:

Jame yra 1024 baitai duomenų EEPROM atmintyje. Jį galima pasiekti kaip atskirą duomenų erdvę, kurioje galima skaityti ir rašyti atskirus baitus.

Įvesties / išvesties atmintis:

Visi įvesties / išvesties įrenginiai ir išoriniai įrenginiai dedami į įvesties / išvesties erdvę. Į įvesties / išvesties vietas galima patekti IN ir OUT instrukcijomis, perkeliant duomenis tarp 32 bendrosios paskirties registrų ir įvesties / išvesties vietos. Įvesties / išvesties registrai, kurių adresas yra 00-1F, yra tiesiogiai prieinami bitais, naudojant SBI ir CBI instrukcijas.

ATmega8

Įvadas

Tai yra 8 bitų CMOS sukurtas AVR šeimos mikrovaldiklis (sukurtas „Atmel Corporation“ 1996 m.) Ir sukurtas remiantis RSIC („Reduced Instruction Set Computer“) architektūra. Pagrindinis jo pranašumas yra tai, kad jame nėra akumuliatoriaus, o bet kurios operacijos rezultatas gali būti saugomas bet kuriame registre, apibrėžtame instrukcija.

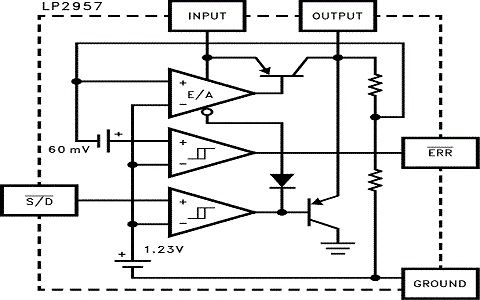

Architektūra

Architektūra

Atmintis

Jį sudaro 8KB „flash“ atminties, 1KB SRAM ir 512 baitų EEPROM. 8K blykstė yra padalinta į 2 dalis - apatinė dalis naudojama kaip įkrovos blykstės dalis, o viršutinė - kaip programos blykstės dalis. SRAM yra 1K baitų, taip pat 1120 baitų bendrosios paskirties registrų ir įvesties / išvesties registrų. Apatinės 32 adresų vietos naudojamos 32 bendrosios paskirties 8 bitų registrams. Kiti 64 adresai naudojami įvesties / išvesties registrams. Visi registrai yra tiesiogiai prijungti prie ALU. EEPROM naudojamas saugoti vartotojo apibrėžtus duomenis.

Įvesties / išvesties prievadai

Jį sudaro 23 įvesties / išvesties linijos su 3 įvesties / išvesties prievadais, pavadintomis B, C ir D. B prievadą sudaro 8 įvesties / išvesties linijas, C prievadą sudaro 7 įvesties / išvesties linijas ir D prievadą sudaro 8 įvesties / išvesties linijas linijos.

Registrai, atitinkantys bet kurį X prievadą (B, C arba D), yra šie:

DDRX : X prievado duomenų krypčių registras

PORTX : X prievado duomenų registras

PINX : X prievado įvesties registras

Laikmačiai ir skaitikliai

Jį sudaro 3 laikmačiai su panašiais režimais. Du iš jų yra 8 bitų, o trečiasis - 16 bitų.

Osciliatoriai

Jame yra vidinis atstatymas ir osciliatorius, leidžiantis pašalinti bet kokio išorinio įvesties poreikį. Vidinis RC osciliatorius sugeba generuoti vidinį laikrodį, kuris gali veikti bet kokiu 1MHz, 2MHz, 4MHz arba 8MHz dažniu, kaip užprogramuota. Jis taip pat palaiko išorinį osciliatorių, kurio maksimalus dažnis yra 16 MHz.

Bendravimas

Jis teikia tiek sinchroninio, tiek asinchroninio duomenų perdavimo schemas per USART (universalų sinchroninį ir asinchroninį imtuvo siųstuvą), t. Y. Ryšį su modemais ir kitais nuosekliaisiais įrenginiais. Jis taip pat palaiko SPI (nuosekliąją periferinę sąsają), naudojamą bendravimui tarp įrenginių, remiantis pagrindinio-vergo metodu. Kitas palaikomas ryšio tipas yra TWI (dviejų laidų sąsaja). Tai leidžia komutuoti bet kuriuos du įrenginius naudojant 2 laidus kartu su bendru įžeminimo ryšiu.

Jame taip pat yra į lustą integruotas palyginimo modulis, kad būtų galima palyginti dvi įtampas, prijungtas prie dviejų „Analog“ lygintuvo įėjimų per išorines mikroschemas.

Jame taip pat yra 6 kanalų ADC, iš kurių 4 turi 10 bitų tikslumą, o 2 - su 8 bitų tikslumu.

Būsenos registras : Joje yra informacija apie šiuo metu vykdomą aritmetinių komandų rinkinį.

„ATmega Pin“ schema :

„ATmega Pin“ schema

Viena iš svarbių „ATmega8“ savybių yra ta, kad, išskyrus 5 kaiščius, visi kiti kaiščiai palaiko du signalus.

- C prievadui naudojami 23,24,25,26,27,28 ir 1 kaiščiai, o B prievadui - 9,10,14,15,16,17,18,19 kaiščiai ir 2,3,4 kaiščiai, 5,6,11,12 yra naudojami D uoste.

- 1 kaištis taip pat yra atstatymo kaištis ir taikant žemo lygio signalą ilgesnį laiką nei minimalus impulso ilgis, bus atstatytas.

- 2 ir 3 kaiščiai taip pat naudojami nuosekliam „USART“ ryšiui.

- 4 ir 5 kaiščiai naudojami kaip išoriniai pertraukimai. Vienas iš jų suveiks, kai bus nustatytas būsenos registro pertraukimo vėliavos bitas, o kitas suveiks tol, kol vyraus pertraukimo sąlyga.

- 9 ir 10 kaiščiai naudojami kaip išorinis osciliatorius, taip pat laikmačio skaitiklių osciliatoriai, kai kristalas yra tiesiogiai sujungtas tarp kaiščių. Kaištis 10 naudojamas krištolo osciliatoriui arba žemo dažnio kristaliniam osciliatoriui. Jei vidinis kalibruotas RC osciliatorius naudojamas kaip laikrodžio šaltinis ir įjungtas asinchroninis laikmatis, šie kaiščiai gali būti naudojami kaip laikmačio osciliatoriaus kaiščiai.

- 19 kaištis naudojamas kaip pagrindinio laikrodžio išvestis, vergo laikrodžio įvestis SPI kanalui.

- 18 kaištis naudojamas kaip pagrindinio laikrodžio įvestis, vergo laikrodžio išvestis.

- 17 kaištis naudojamas kaip pagrindinių duomenų išvestis, vergo duomenų įvedimas SPI kanalui. Jis naudojamas kaip įvestis, kai įgalinamas vergo, ir yra dvikryptis, kai įgalinamas pagrindinis. Šis kaištis taip pat gali būti naudojamas kaip išvesties palyginimo atitikties išvestis, kuri naudojama kaip išorinis laikmačio / skaitiklio palyginimo atitikties išėjimas.

- Pin16 naudojamas kaip vergo pasirinkimo įvestis. Jis taip pat gali būti naudojamas kaip laikmačio / skaitiklio1 palyginimo atitikimas sukonfigūravus PB2 kaištį kaip išvestį.

- Pin15 gali būti naudojamas kaip išorinis laikmačio / skaitiklio palyginimo A atitikmuo.

- 23–28 kaiščiai naudojami ADC kanalams. Kaištis 27 taip pat gali būti naudojamas kaip nuosekliosios sąsajos laikrodis, o kaištis 28 - kaip nuosekliosios sąsajos duomenys

- 13 ir 12 kaiščiai naudojami kaip analoginio komparatoriaus įėjimai.

- 11 ir 6 kaiščiai naudojami kaip laikmačio / skaitiklio šaltiniai.

Mikrovaldiklių miego režimai

Mikrovaldiklis veikia 6 miego režimais.

- Laukimo režimas: Jis sustabdo procesoriaus veikimą, tačiau leidžia valdyti SPI, USART, ADC, TWI, laikmatį / skaitiklį ir „Watchdog“ bei pertraukia sistemą. Tai pasiekiama nustačius MCU registro vėliavos SM0 – SM2 bitus į nulį.

- ADC triukšmo mažinimo režimas : Jis sustabdo procesorių, bet leidžia ADC, išorinius pertraukimus, laikmatį / skaitiklį2 ir budėjimo šunį.

- Išjungimo režimas : Jis įgalina išorinius pertraukimus, 2 laidų nuosekliąją sąsają, budėjimo šunį ir išjungia išorinį osciliatorių. Jis sustabdo visus sugeneruotus laikrodžius.

- Energijos taupymo režimas : Jis naudojamas, kai laikmatis / skaitiklis nustatomas asinchroniškai. Jis sustabdo visus laikrodžius, išskyrus laikrodžiusASY.

- Budėjimo režimas : Šiuo režimu osciliatoriui leidžiama veikti sustabdžius visas kitas operacijas.

„Atmega8“ programos

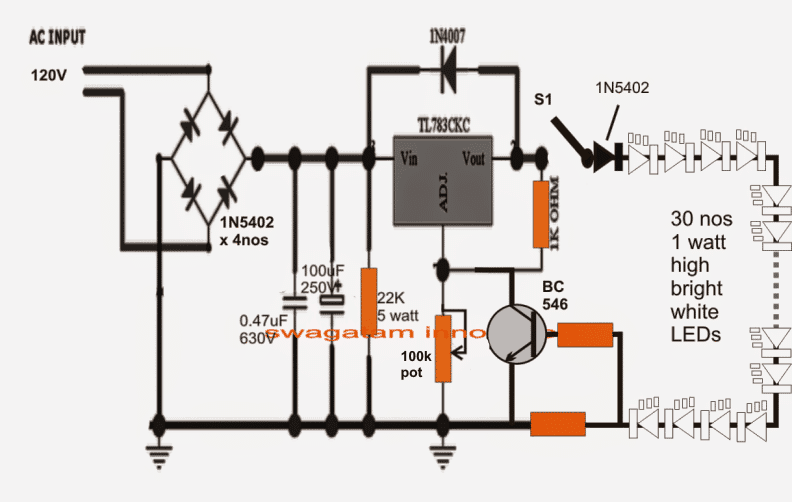

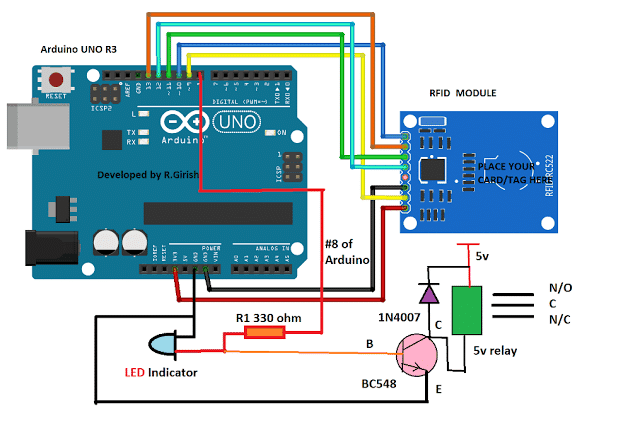

Mirksintis šviesos diodas

Mirksinti „LEd“ schema

Programa parašyta naudojant C kalbą ir pirmiausia sudaryta kaip .c failas. Programinės įrangos įrankis ATMEL pavers šį failą į dvejetainį ELF objekto failą. Tada jis vėl paverčiamas į hex failą. Tada hex failas perduodamas mikrovaldikliui naudojant AVR dude programą.

Nuotraukų kreditas:

- 40 kontaktų DIP „ATmega32“ nuotrauka wikimedia

- ISP programuotojo schema pagal šiandien

- Architektūra šiandien

- „ATmega Pin“ diagrama atmega32-avr