Instrukcijų rinkinio arba komandų rinkinio architektūra - tai kompiuterio struktūra, suteikianti komandas kompiuteriui, kuris nurodo kompiuterį apdoroti duomenis. Instrukcijų rinkinį sudaro instrukcijos, adresavimo režimai, vietiniai duomenų tipai, registrai, pertraukimas, išimčių tvarkymas ir atminties architektūra. Instrukcijų rinkinį galima imituoti programinėje įrangoje naudojant vertėją arba įmontuotą į procesoriaus aparatinę įrangą. Instrukcijų rinkinio architektūra gali būti laikoma riba tarp programinės ir aparatinės įrangos. Mikrovaldiklių klasifikacija ir mikroprocesoriai gali būti atliekami remiantis RISC ir CISC instrukcijų rinkinio architektūra.

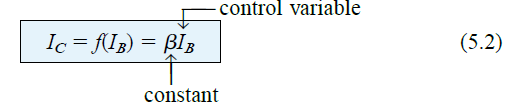

Procesoriaus instrukcijų rinkinys

Instrukcijų rinkinys nurodo procesoriaus funkcionalumą, įskaitant procesoriaus palaikomas operacijas, procesoriaus saugojimo mechanizmus ir programų sudarymo procesoriui būdą.

Kas yra RISC ir CISC?

The RISC ir CISC galima išplėsti taip:

RISC reiškia sumažinto nurodymų kompiuterio kompiuterį ir

CISC reiškia sudėtingą instrukcijų rinkinį.

RISC (Reduced Instruction Set Computer) architektūra

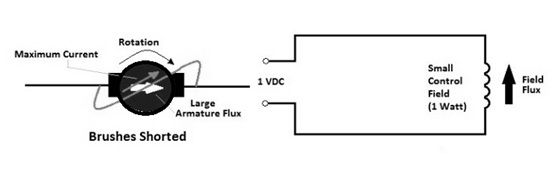

RISC architektūra

The mikrovaldiklio architektūra kuris naudoja mažą ir labai optimizuotą instrukcijų rinkinį, vadinamas „Reduced Instruction Set Computer“ arba tiesiog vadinamas RISC. Jis taip pat vadinamas LOAD / STORE architektūra.

Aštuntojo dešimtmečio pabaigoje ir devintojo dešimtmečio pradžioje RISC projektai pirmiausia buvo kuriami iš Stanfordo, UC-Berkley ir IBM. Johnas Coke'as iš IBM tyrimų grupės sukūrė RISC sumažindamas instrukcijų skaičių, reikalingą skaičiavimams apdoroti greičiau nei CISC. RISC architektūra yra greitesnė, o mikroschemos, reikalingos RISC architektūrai gaminti, taip pat yra pigesnės, palyginti su CISC architektūra.

Tipinės RISC architektūros ypatybės

- RISC vamzdynų technika vienu metu vykdo kelias instrukcijų dalis ar etapus taip, kad kiekviena instrukcija procesoriuje būtų optimizuota. Taigi RISC procesoriai turi vieno ciklo „Laikrodis pagal instrukciją“, ir tai vadinama vieno ciklo vykdymu.

- Tai optimizuoja registro naudojimas esant daugiau registrų skaičiui RISC ir daugiau sąveikos atmintyje, galima išvengti.

- Paprastus adresavimo režimus, net sudėtingus adresus galima atlikti naudojant aritmetiką IR / ARBA loginės operacijos .

- Tai supaprastina kompiliatoriaus dizainą, naudodamas identiškus bendrosios paskirties registrus, kurie leidžia naudoti bet kurį registrą bet kuriame kontekste.

- Norint efektyviai naudoti registrus ir optimizuoti vamzdynų naudojimą, reikalingas sumažintas instrukcijų rinkinys.

- Sumažinamas opkodui naudojamų bitų skaičius.

- Apskritai RISC yra 32 ar daugiau registrų.

RISC procesoriaus architektūros pranašumai

- Dėl nedidelio RISC instrukcijų rinkinio aukšto lygio kalbų kompiliatoriai gali sukurti efektyvesnį kodą.

- RISC leidžia laisvai naudoti erdvę mikroprocesoriai dėl savo paprastumo.

- Užuot naudoję „Stack“, daugelis RISC procesorių naudoja registrus argumentams perduoti ir vietiniams kintamiesiems laikyti.

- RISC funkcijos naudoja tik keletą parametrų, todėl RISC procesoriai negali naudoti skambučių nurodymų, todėl naudoja fiksuoto ilgio instrukcijas, kurias lengva perduoti.

- Operacijos greitis gali būti maksimalus, o vykdymo laikas - kuo trumpesnis.

- Reikia labai mažai komandų formatų (mažiau nei keturi), kelių instrukcijų (apie 150) ir kelių adresavimo režimų (mažiau nei keturi).

RISC procesoriaus architektūros trūkumai

- Pailgėjus instrukcijų trukmei, RISC procesoriai tampa sudėtingesni vykdyti dėl savo simbolių ciklo kiekvienoje instrukcijoje.

- RISC procesorių našumas labiausiai priklauso nuo kompiliatoriaus ar programuotojo, nes kompiliatoriaus žinios vaidina svarbų vaidmenį, tuo pačiu konvertuojant CISC kodą į RISC kodą, todėl sugeneruoto kodo kokybė priklauso nuo kompiliatoriaus.

- Planuojant CISC kodą pakeisti į RISC kodą, vadinamą kodo išplėtimu, dydis padidės. Šio kodo išplėtimo kokybė vėl priklausys nuo kompiliatoriaus ir nuo mašinos instrukcijų rinkinio.

- Pirmojo lygio RISC procesorių talpykla taip pat yra RISC trūkumas, kai šie procesoriai turi didelę atminties talpyklą pačioje mikroschemoje. Norėdami maitinti instrukcijas, jie reikalauja labai greitos atminties sistemos .

CISC („Complex Instruction Set Computer“) architektūra

Pagrindinis CISC procesoriaus architektūros tikslas yra atlikti užduotį naudojant mažiau surinkimo linijų. Šiuo tikslu procesorius sukurtas atlikti keletą operacijų. Kompleksinis nurodymas taip pat vadinamas MULT, kuris veikia atminties bankai kompiuterio tiesiogiai, nepriversdamas kompiliatoriaus atlikti saugojimo ir įkėlimo funkcijų.

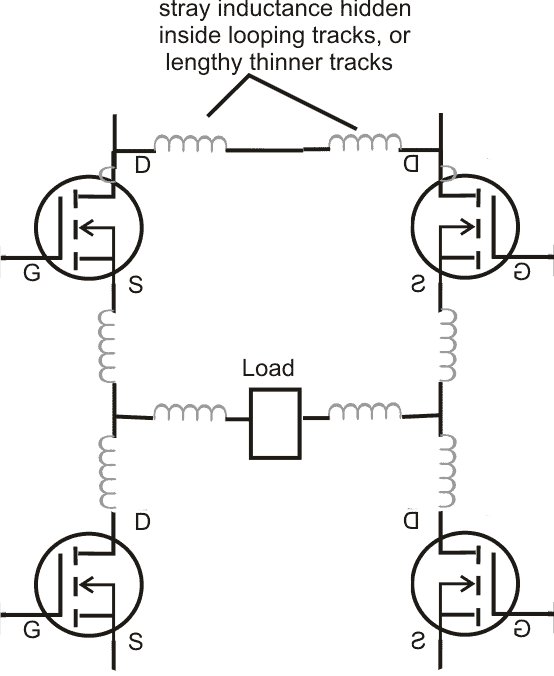

CISC architektūra

CISC architektūros ypatybės

- Norėdami supaprastinti kompiuterio architektūrą, CISC palaiko mikroprogramavimą.

- CISC turi daugiau iš anksto nustatytų instrukcijų, todėl aukšto lygio kalbas lengva kurti ir įgyvendinti.

- CISC sudaro mažesnis registrų skaičius ir didesnis adresavimo režimų skaičius, paprastai nuo 5 iki 20.

- CISC procesorius instrukcijų vykdymui užima skirtingą ciklo laiką - kelių laikrodžių ciklus.

- Dėl sudėtingų CISC instrukcijų rinkinio vamzdynų technika yra labai sudėtinga.

- CISC sudaro daugiau instrukcijų, paprastai nuo 100 iki 250.

- Specialios instrukcijos naudojamos labai retai.

- Operantai atmintyje yra valdomi instrukcijomis.

CISC architektūros pranašumai

- Kiekviena mašininės kalbos instrukcija yra sugrupuota į mikrokodo komandą ir atitinkamai vykdoma, tada saugoma įmontuota pagrindinio procesoriaus atmintyje, vadinama mikrokodo įgyvendinimu.

- Kadangi mikrokodo atmintis yra greitesnė nei pagrindinė atmintis, mikrokodų komandų rinkinį galima įdiegti nemažinant greičio, palyginti su laidiniu įgyvendinimu.

- Visą naują komandų rinkinį galima tvarkyti modifikuojant mikroprogramos dizainą.

- CISC, programai įgyvendinti reikalingų instrukcijų skaičių galima sumažinti kuriant turtingus instrukcijų rinkinius, taip pat galima priversti efektyviau naudoti lėtą pagrindinę atmintį.

- Dėl supaprastinto instrukcijų rinkinio, kurį sudaro visos ankstesnės instrukcijos, mikrokodavimas tampa lengvas.

CISC trūkumai

- Skirtingomis instrukcijomis užimtas laikrodžio laikas bus skirtingas - dėl to sulėtėja mašinos veikimas.

- Komandų rinkinio sudėtingumas ir lusto aparatūra didėja, nes kiekvieną naują procesoriaus versiją sudaro ankstesnių kartų pogrupis.

- Tik 20% esamų instrukcijų yra naudojamos įprastame programavimo renginyje, nors egzistuoja daugybė specializuotų instrukcijų, kurios net nėra dažnai naudojamos.

- Sąlyginiai kodai nustatomi CISC instrukcijose kaip šalutinis kiekvienos instrukcijos poveikis, kuriam reikia laiko šiam nustatymui - ir, kai sekanti instrukcija pakeičia sąlygų kodo bitus, kompiliatorius turi ištirti sąlygų kodo bitus, kol tai neįvyks.

RISC vs. CISC

- Programuotojas gali užkirsti kelią švaistymo ciklams pašalindamas nereikalingą kodą RISC, tačiau, nors naudojant CISC kodą, dėl CISC neefektyvumo, švaistomi ciklai.

- RISC kiekviena instrukcija skirta atlikti nedidelę užduotį, kad, norint atlikti sudėtingą užduotį, kartu būtų naudojamos kelios mažos instrukcijos, o norint atlikti tą pačią užduotį naudojant CISC, reikalingos tik kelios instrukcijos, nes ji gali atlikti sudėtingą užduotį nes instrukcijos yra panašios į aukštos kalbos kodą.

- CISC paprastai naudojamas kompiuteriams, o RISC - išmaniesiems telefonams, planšetiniams kompiuteriams ir kitiems elektroniniams prietaisams.

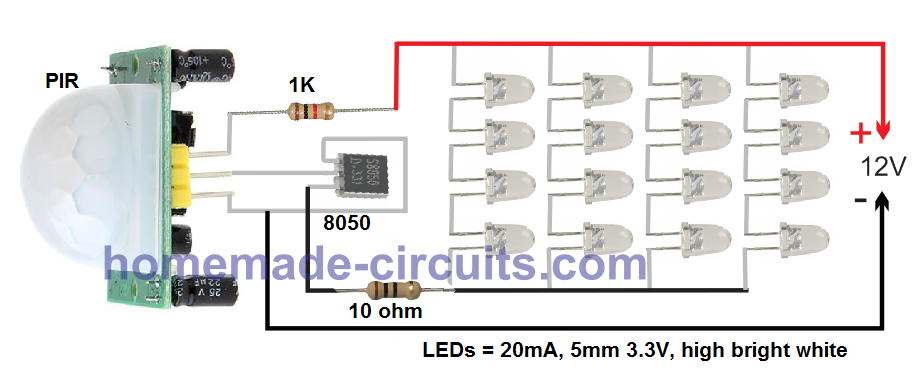

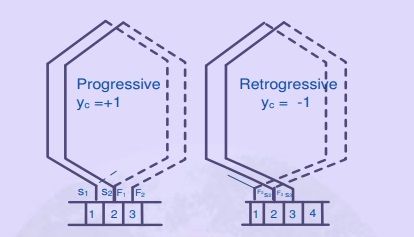

Šis paveikslėlis rodo daugiau skirtumų tarp RISC ir CISC

RISC vs. CISC

Taigi šiame straipsnyje aptariamos RISC ir CISC architektūros ypatybės, susijusios su RISC ir CISC procesorių architektūros privalumais ir trūkumais, bei RISC ir CISC architektūrų skirtumai trumpai sugalvojant. Norėdami gauti daugiau informacijos apie RISC ir CISC architektūras, pateikite savo užklausas komentuodami žemiau.

Nuotraukų kreditai:

- Procesoriaus instrukcijų rinkinį pateikė arstechnica

- RISC architektūra lsi-konkursas

- RISC ir CISC pagal csar paskyrimas