Šiame straipsnyje paaiškinama pulso pločio moduliacijos generavimas signalai su kintamu darbo ciklu FPGA naudojant VHDL. PWM turi fiksuotą dažnį ir kintamą įtampą. Šiame straipsnyje taip pat aptariamas skaitmeninio laikrodžio tvarkytuvas, kaip sumažinti laikrodžio dažnį mažinant laikrodžio signalo kreivumą. Fiksuotas dažnis naudojamas įvesties duomenims, kurie generuoja PWM signalus, naudodami lyginamąjį dažnį. Elektronikos kompanijos kuria savo gaminiams skirtą aparatinę įrangą pagal savo standartus ir protokolus, todėl galutiniams vartotojams yra sudėtinga pertvarkyti aparatinę įrangą pagal jų poreikius. Šis reikalavimas aparatinei įrangai lėmė naujo kliento konfigūruojamo segmento augimą programuojami lauko integruoti grandynai, vadinami FPGA .

Impulso pločio moduliacija (PWM)

Impulso pločio moduliacija plačiai naudojama komunikacijos ir valdymo sistemos . Impulso pločio moduliacija gali būti sukurta naudojant skirtingus metodus valdymo sistemose. Čia, šiame straipsnyje, PWM generuojamas naudojant aparatūros aprašymo kalbą (VHDL) ir įgyvendinamas FPGA. PWM diegimas FPGA gali greičiau apdoroti duomenis, o valdiklio architektūrą galima optimizuoti pagal erdvę ar greitį.

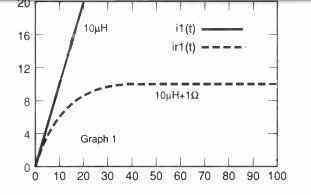

PWM yra metodas, suteikiantis logiką „0“ ir logiką „1“ kontroliuojamam laikotarpiui. Tai signalo šaltinis, apimantis jo darbo ciklo moduliavimą, siekiant kontroliuoti į apkrovą siunčiamos galios kiekį. PWM metu kvadratinės bangos laikotarpis yra pastovus, o laikas, kuriam signalas išlieka AUKŠTAS, yra įvairus.

PWM generuoja impulsus savo išėjime taip, kad vidutinė HIGHs ir LOWs vertė būtų proporcinga PWM įėjimui. Signalo veikimo ciklas gali būti įvairus. PWM signalas yra pastovaus periodo kvadratinė banga su skirtingu darbo ciklu. Tai yra, PWM signalo dažnis yra pastovus, tačiau signalo laikotarpis išlieka didelis ir skiriasi, kaip parodyta.

PWM signalas

VHDL

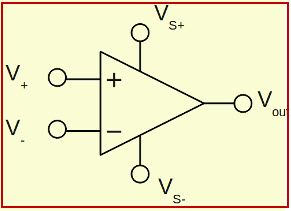

VHDL yra kalba, naudojama apibūdinti žmonių elgesį skaitmeninių grandinių dizainas . VHDL naudoja pramonės atstovai ir mokslininkai skaitmeninių grandinių modeliavimui. Jo dizainą galima imituoti ir išversti tokia forma, kuri yra tinkama įgyvendinti aparatinėje įrangoje.

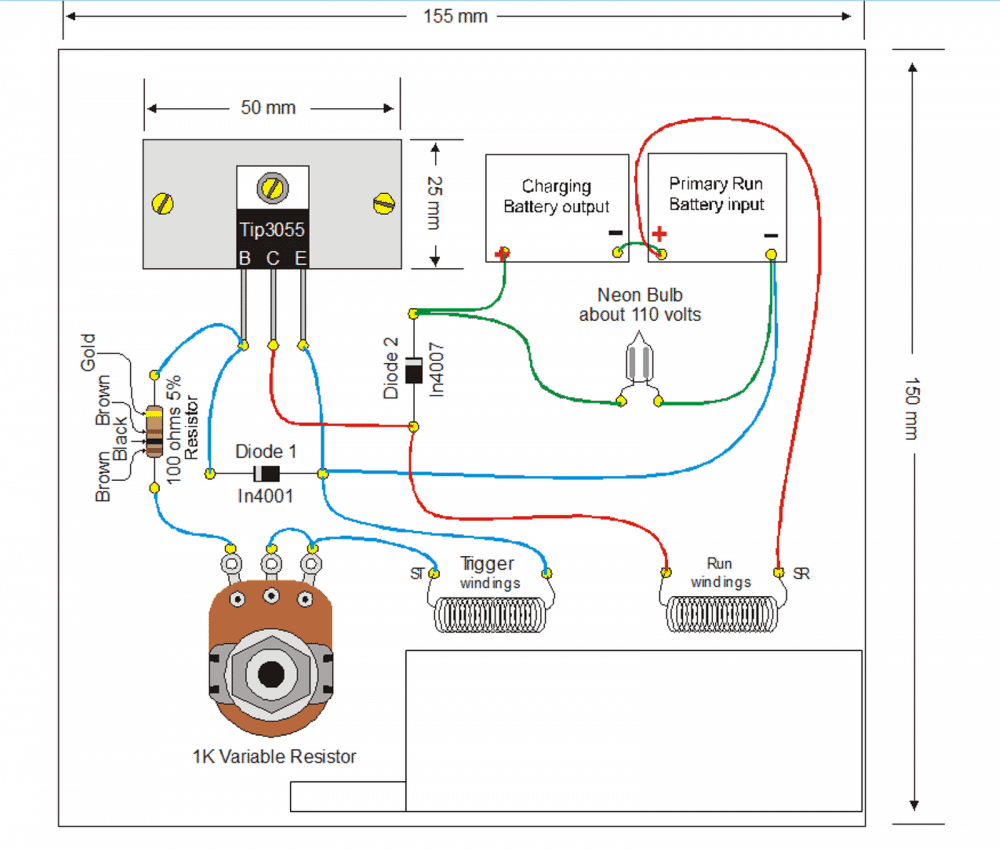

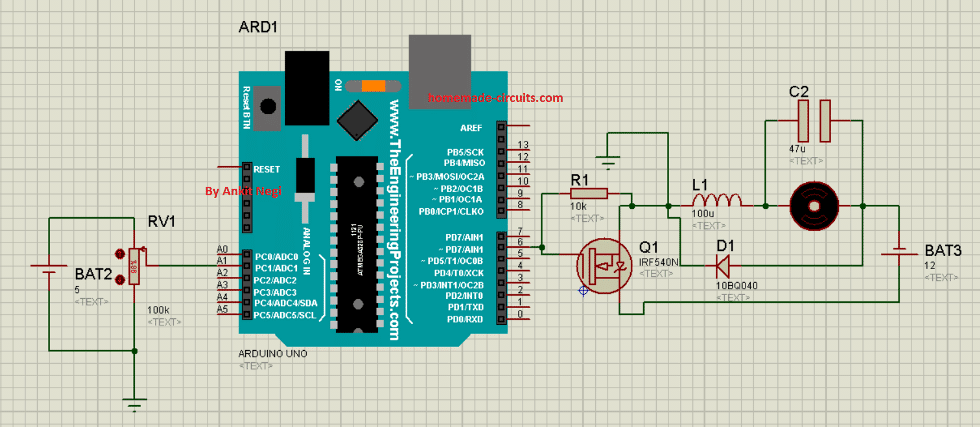

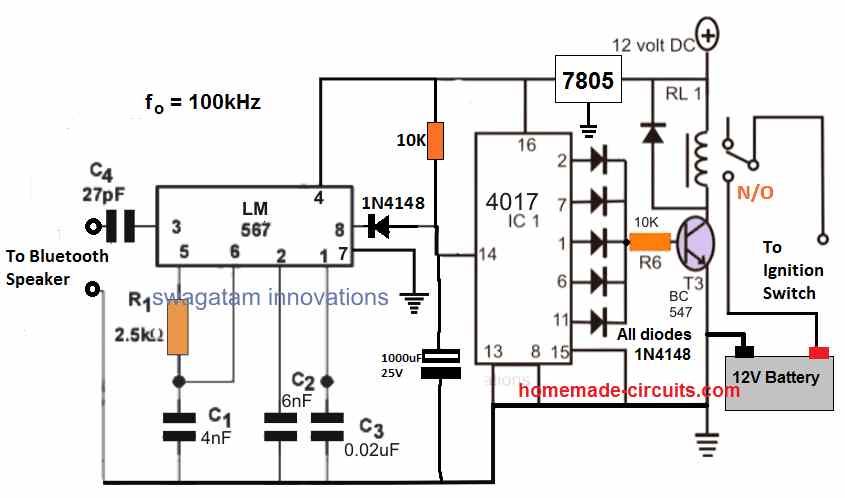

PWM architektūra

Norėdami sukurti įvesties duomenis, kad generuotumėte PWM, naudodamiesi greitaeigiu N bitų laisvosios eigos skaitikliu, kurio išvestis palyginama su registro išvestimi ir naudojant palyginamąją priemonę išsaugomas norimas įvesties darbo ciklas. Lyginamasis išvestis nustatyta į 1, kai abi šios vertės yra vienodos. Ši lyginamoji išvestis naudojama nustatyti RS skląstį. Perpildymo signalas iš skaitiklio naudojamas RS fiksatoriui atstatyti. RS skląsčio išvestis suteikia norimą PWM išvestį. Šis perpildymo signalas taip pat naudojamas įkelti naują N bitų darbo ciklą į registrą. PWM turi fiksuotą dažnį ir kintamą įtampą. Ši įtampos vertė keičiasi nuo 0V iki 5 V.

PWM signalas su kintamu darbo ciklu

Pagrindiniam PWM generuojami signalai, o tai suteikia PWM išvestį, reikalingas lygintuvas, lyginantis dvi reikšmes. Pirmoji reikšmė reiškia kvadratinį signalą, kurį generuoja N bitų skaitiklis, o antroji - kvadratinį signalą, kuriame yra informacija apie darbo ciklą. Skaitiklis sukuria apkrovos signalą, kai tik yra perpildymas. Kai apkrovos signalas tampa aktyvus, registras įkelia naują darbo ciklo vertę. Apkrovos signalas taip pat naudojamas fiksatoriui atstatyti. Spynos išėjimas yra PWM signalas. Tai kinta keičiantis darbo ciklo vertei.

Kas yra FPGA?

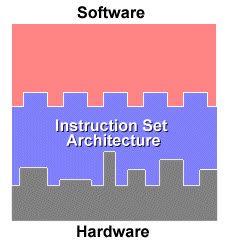

FPGA yra lauko programuojamas vartų masyvas. Tai yra prietaiso tipas, plačiai naudojamas elektroninėse grandinėse. FPGA yra puslaidininkiniai įtaisai kuriuose yra programuojami loginiai blokai ir sujungimo grandinės. Pagaminus, jį galima užprogramuoti arba perprogramuoti pagal reikiamą funkcionalumą.

FPGA

FPGA pagrindai

Kai gaminama plokštė ir jei jos dalyje yra FPGA. Tai užprogramuota gamybos proceso metu ir vėliau gali būti perprogramuota vėliau, kad būtų sukurtas atnaujinimas arba būtini pakeitimai. Ši FPGA funkcija daro ją unikalią iš ASIC. Programos specifiniai integriniai grandynai (ASIC) yra gaminami pagal užsakymą konkrečiai projektavimo užduočiai. Anksčiau FPGA buvo naudojami kuriant mažą greitį, sudėtingumą ir garsumo dizainą, tačiau šiandien FPGA lengvai nustums veikimo barjerą iki 500MHz.

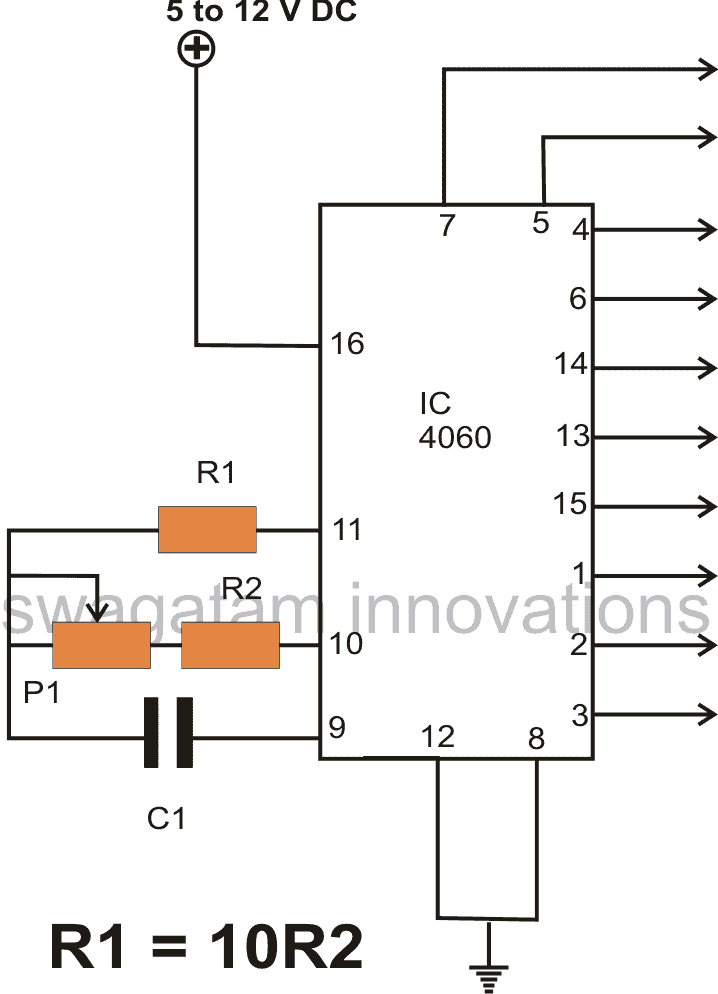

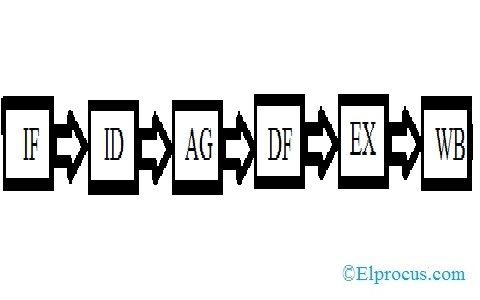

Mikrovaldikliuose mikroschema yra skirta klientui ir jie turi parašyti programinę įrangą ir sukompiliuoti ją į hex failą, kad būtų galima įkelti į mikrovaldiklį. Šią programinę įrangą galima lengvai pakeisti, nes ji saugoma „flash“ atmintyje. FPGA nėra procesoriaus, kuris galėtų paleisti programinę įrangą, o mes esame tie, kurie projektuoja grandinę. Mes galime sukonfigūruoti FPGA taip paprasta, kaip „AND gate“ arba kompleksą, kaip kelių branduolių procesorių. Norėdami sukurti dizainą, mes rašome aparatūros aprašymo kalbą (HDL), kuri yra dviejų tipų - „Verilog“ ir „VHDL“. Tada DTL susintetinamas į šiek tiek failą naudojant BITGEN, kad sukonfigūruotumėte FPGA. FPGA konfigūraciją saugo RAM, ty konfigūracija prarandama, kai nėra maitinimo jungties. Taigi jie turi būti sukonfigūruoti kiekvieną kartą, kai tiekiama energija.

FPGA architektūra

FPGA yra surenkamos silicio mikroschemos, kurias galima programuoti elektra, kad būtų galima įgyvendinti skaitmeninius dizainus. Pirmoji statinės atminties pagrindu sukurta FPGA, vadinama SRAM, naudojama tiek logikos, tiek sujungimo konfigūravimui naudojant konfigūracijos bitų srautą. Šiandienos šiuolaikinėje EPGA yra maždaug 3 30 000 loginių blokų ir apie 1100 įėjimų ir išėjimų.

FPGA architektūra

FPGA architektūrą sudaro trys pagrindiniai komponentai

- Programuojami logikos blokai, kurie įgyvendina logikos funkcijas

- Programuojamas maršrutas (sujungia), kuris įgyvendina funkcijas

- Įvesties / išvesties blokai, naudojami užmezgant jungtis

PWM signalų taikymas

PWM signalai plačiai naudojami valdymo programose. Kaip nuolatinės srovės variklių, valdymo vožtuvų, siurblių, hidraulikos ir kt. Valdymas. Čia yra keletas PWM signalų taikymo būdų.

- Šildymo sistemos, kurių lėtas laikas yra nuo 10 iki 100 Hz arba didesnis.

- 5–10 kHz nuolatinės srovės elektros varikliai

- Maitinimo šaltiniai arba garso stiprintuvai nuo 20 iki 200 KHz.

Šis straipsnis yra apie generuoti PWM signalus su kintamu darbo ciklu naudojant FPGA. Be to, dėl bet kokios pagalbos dėl elektroninių projektų ar abejonių dėl šio straipsnio galite susisiekti su mumis pakomentuodami toliau pateiktą komentarų skyrių.