Pirmą kartą ECL (emitter coupled logic) 1956 m. rugpjūtį IBM išrado Hannon S. Yourke. Ši logika taip pat žinoma kaip dabartinio režimo logika, naudojama IBM 7090 ir 7094 kompiuteriuose. ECL šeima yra labai greita, palyginti su skaitmeninė logika šeimos. Paprastai ši loginė šeima suteikia sklidimo delsą, mažesnę nei 1 ns. Tai loginė šeima, pagrįsta dvipoliais tranzistoriais. Tai greičiausia loginės šeimos grandinė, kuri yra prieinama kuriant įprastą logikos sistemą. Šiame straipsnyje aptariama an emitteriu sujungta logika-grandinė , darbas su programomis.

Kas yra „emitter Coupled Logic“?

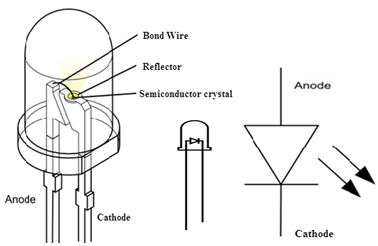

Su emitteriu susieta logika yra geriausia BJT - pagrįsta logikos šeima, naudojama tradiciniame logikos sistemos projekte. Kartais ji taip pat vadinama dabartinio režimo logika, kuri yra labai didelės spartos skaitmeninė technologija. Paprastai ECL laikomas greičiausiu loginiu IC, kai jis pasiekia greitą veikimą naudodamas labai mažą įtampos svyravimą ir taip pat išvengdamas tranzistorių patekimo į prisotinimo sritį.

ECL įgyvendinimas naudoja teigiamą maitinimo įtampą, vadinamą PECL arba teigiamąja ECL. Ankstyvuosiuose ECL vartuose dėl atsparumo triukšmui naudojamas neigiamas įtampos tiekimas. Po to teigiamas nuorodas turintis ECL tapo labai žinomas dėl labiau suderinamų loginių lygių, palyginti su TTL logikos šeimomis.

Su emitteriu sujungta logika išsklaido didžiulį statinės galios kiekį, tačiau bendras jos srovės suvartojimas yra mažas, palyginti su CMOS aukštais dažniais. Taigi, ECL daugiausia naudinga laikrodžio paskirstymo grandinėse ir aukšto dažnio programose.

Emitter Coupled Logic funkcijos

Dėl ECL funkcijų jie bus naudojami daugelyje didelio našumo pagrįstų programų.

- ECL suteikia du išėjimus, kurie visada papildo vienas kitą, nes grandinės veikimas pagrįstas diferencialiniu stiprintuvu.

- Ši loginė šeima daugiausia tinka monolitiniams gamybos būdams, nes loginiai lygiai priklauso nuo rezistorių santykio.

- ECL šeimos įrenginiai generuoja tinkamą ir papildomą siūlomos funkcijos išvestį nenaudodami jokių išorinių keitiklių. Dėl to sumažėja paketų skaičius ir energijos poreikis, taip pat sumažėja problemų, kylančių dėl laiko vėlavimo.

- Diferencialinio stiprintuvo konstrukcijos ECL įrenginiai siūlo platų veikimo lankstumą, todėl ECL grandinės leidžia naudoti tiek kaip skaitmenines, tiek kaip linijines grandines.

- ECL vartų konstrukcija paprastai turi didelę ir mažą įėjimo varžą, kuri yra ypač palanki norint pasiekti didelį ventiliatorių ir pavaros pajėgumus.

- ECL įrenginiai generuoja nuolatinę srovės nutekėjimą iš maitinimo šaltinio, kad būtų supaprastinta maitinimo šaltinio konstrukcija.

- ECL įrenginiai, įskaitant atvirojo emiterio išėjimus, tiesiog leidžia įtraukti perdavimo linijos pavaros pajėgumus.

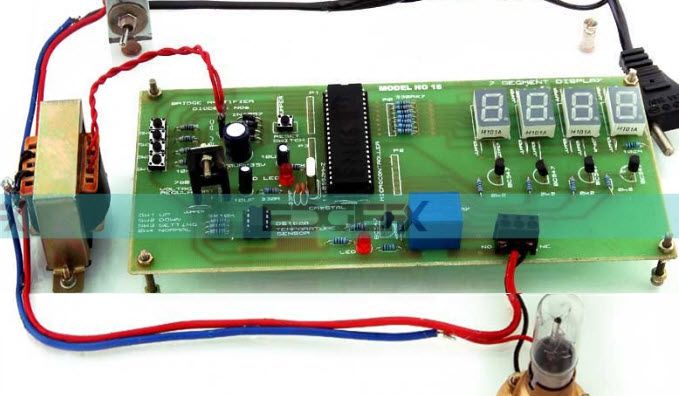

Emiterio prijungta loginė grandinė

Žemiau parodyta keitiklio su emitteriu sujungta loginė grandinė, kuri suprojektuota su rezistoriais ir tranzistoriais. Šioje grandinėje dviejų tranzistorių emiterio gnybtai tiesiog prijungiami prie srovę ribojančios varžos RE, kuri naudojama siekiant išvengti tranzistoriaus prisotinimo. Čia tranzistoriaus išvestis paimama iš kolektoriaus gnybto, o ne iš emiterio gnybto. Šioje grandinėje yra du išėjimai Vout (invertuojantis išėjimas) ir Vout2 (neinvertuojantis išėjimas) ir įvesties gnybtas, pvz., Vin, kur suteikiama aukšta arba žema įvestis. +Vcc = 5V.

Kaip veikia Emitter Coupled Logic?

Su emitteriu susietos logikos veikimas yra toks, kad kiekvieną kartą, kai ECL grandinei suteikiamas HIGH įėjimas, „Q1“ tranzistorius ĮJUNGTAS, o Q2 tranzistorius IŠJUNGTAS, tačiau Q1 tranzistorius nėra prisotintas. Taigi dėl to VOUT2 išvestis bus padidinta iki HIGH, o VOUT1 išvesties vertė bus LOW, nes sumažės R1.

Panašiai, kai ECL suteikta VIN reikšmė yra MAŽA, Q1 tranzistorius IŠJUNGTAS, o Q2 tranzistorius ĮJUNGTAS. Taigi, Q2 tranzistorius nepateks į prisotinimą. Dėl to VOUT1 išvestis bus ištraukta AUKŠTA, o VOUT2 išvesties vertė bus maža dėl R2 pasipriešinimo kritimo.

Pažiūrėkime, kaip tranzistorius Q1 ir Q2 įsijungia ir išsijungia, kai įjungiama įtampa.

Du tranzistoriai, tokie kaip Q1 ir Q2, šioje grandinėje yra sujungti kaip diferencialinis stiprintuvas bendru emiterio rezistorius.

Šio pavyzdžio grandinės įtampa yra VCC = 5,0, VBB = 4,0 ir VEE = 0 V. Įvesties AUKŠTO ir žemo lygio reikšmės tiesiog apibrėžiamos kaip 4,4 V ir 3,6 V. Tiesą sakant, ši grandinė sukuria 0,6 volto aukštesnius lygius LOW ir HIGH; tačiau tai ištaisoma tikrose ECL grandinėse.

Kai Vin yra AUKŠTAS, Q1 tranzistorius įjungiamas, tačiau nėra prisotintas, o Q2 tranzistorius išjungiamas. Taigi, išėjimo įtampa, tokia kaip VOUT2, per R2 rezistorių ištraukiama iki 5 V ir gali būti parodyta, kad įtampos kritimas per R1 rezistorių yra apie 0,8 V, todėl VOUT1 = 4,2 V (LOW). Be to, VE = VOUT1 - VQ1 => 4,2 V - 0,4 V = 3,8 V, nes tranzistorius Q1 yra visiškai įjungtas.

Kai Vin yra LOW, Q2 tranzistorius bus įjungtas, bet neprisotintas, o Q1 tranzistorius IŠJUNGTAS. Todėl VOUT1 ištraukiamas iki 5,0 V naudojant R1 rezistorių ir galima parodyti, kad VOUT2 yra 4,2 V. Taip pat VE => VOUT2 – VQ2 => 4,2 V – 0,8 V => 3,4 V, nes tranzistorius Q2 įjungtas.

ECL du tranzistoriai niekada nėra prisotinti, nes t įvesties / išvesties įtampos svyravimai yra gana maži, pavyzdžiui, 0,8 V ir įvesties varža yra didelė, o išėjimo varža yra maža. Tai padeda ECL veikti greičiau su trumpesniu sklidimo delsos laiku.

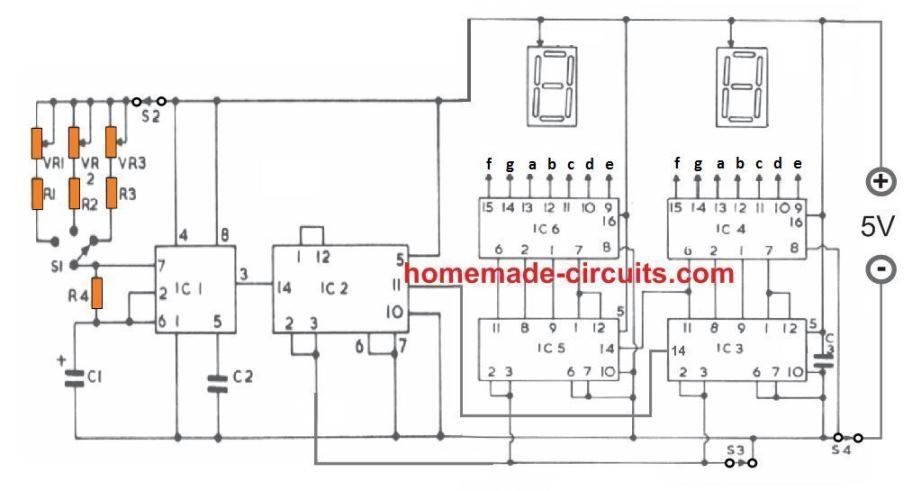

Dviejų įvesties emiterių sujungta loginė ARBA/NOR vartų grandinė

Dviejų įvesties emiterių susietos loginės ARBA/NOR vartų grandinė parodyta žemiau. Ši grandinė sukurta modifikuojant aukščiau pateiktą keitiklio grandinę. Modifikacija atliekama pridedant papildomą tranzistorių įvesties pusėje.

Šios grandinės veikimas yra labai paprastas. Kai tiek Q1, tiek Q2 tranzistorių įėjimai yra žemi, išvestis1 (Vout1) bus aukšta. Taigi, šis Vout1 atitinka NOR vartų išvestį.

Tuo pačiu metu, jei Q3 tranzistorius yra įjungtas, tada antrasis išėjimas (Vout2) bus AUKŠTAS. Taigi, ši Vou2 išvestis atitinka OR vartų išvestį.

Lygiai taip pat, jei abu Q1 ir Q2 tranzistorių įėjimai yra AUKŠTI, tada jis įjungs Q1 ir Q2 tranzistorius ir suteiks žemą išvestį VOUT1 gnybte.

Jei Q3 tranzistorius yra IŠJUNGTAS šios operacijos metu, jis užtikrins didelę galią VOUT2 gnybte. Taigi, tiesos lentelė OR/NOR vartams pateikta žemiau.

|

Įėjimai |

Įėjimai | ARBA |

NOR |

|

A |

B | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Emiter-Coupled loginės charakteristikos

ECL charakteristikos yra šios.

- Palyginti su TTL, ECL sklidimo laikas yra greitesnis nuo 0,5 iki 2 ns. Tačiau emiterio susietos loginės galios išsklaidymas yra didesnis, palyginti su TTL, pavyzdžiui, 30 mW.

- ECL įvesties / išvesties įtampa svyruoja, pavyzdžiui, 0,8.

- ECL įvesties varža yra didelė, o išėjimo varža yra maža; vadinasi, tranzistorius labai greitai keičia savo būsenas.

- ECL ventiliatoriaus išleidimo pajėgumas yra didelis, o vartų vėlavimai yra maži.

- ECL o/p logika keičiasi iš LOW į AUKŠTĄ, tačiau šių būsenų įtampos lygiai skirsis tarp TTL ir EC.

- ECL atsparumas triukšmui yra 0,4 V.

Privalumai ir trūkumai

The su emitteriu susietos logikos pranašumai aptariami toliau.

- ECL ventiliatoriaus išėjimas yra 25, kuris yra geresnis, palyginti su TTL, ir yra žemas, palyginti su CMOS.

- Vidutinis ECL sklidimo delsos laikas yra nuo 1 iki 4 ns, o tai yra geresnis, palyginti su CMOS ir

- TTL. Taigi ji vadinama greičiausia logine šeima.

- Kai emiterio BJT yra sujungti logikos vartai dirba aktyviame regione, tada jie turi didžiausią greitį, palyginti su visomis loginėmis šeimomis.

- ECL vartai generuoja papildomus išėjimus.

- Maitinimo laiduose nėra srovės perjungimo smaigalių.

- Išėjimus galima sujungti kartu, kad būtų galima atlikti laidinio ARBA funkciją.

- ECL parametrai per temperatūrą labai nesikeičia.

- „Nr. iš vienintelio lusto pasiekiamų funkcijų yra daug.

The su emiteriu susietos logikos trūkumai aptariami toliau.

- Jis turi labai mažesnę triukšmo ribą, ty ± 200 mV.

- Galios išsklaidymas yra didelis, palyginti su kitais loginiais vartais.

- Norint susieti su kitomis loginėmis šeimomis, būtini lygių perjungikliai.

- Fanout riboja talpinę apkrovą.

- Palyginti su TTL , ECL vartai yra brangūs.

- Palyginti su CMOS ir TTL, ECL atsparumas triukšmui yra blogiausias.

Programos

Su emitteriu susietos logikos taikymai yra šie.

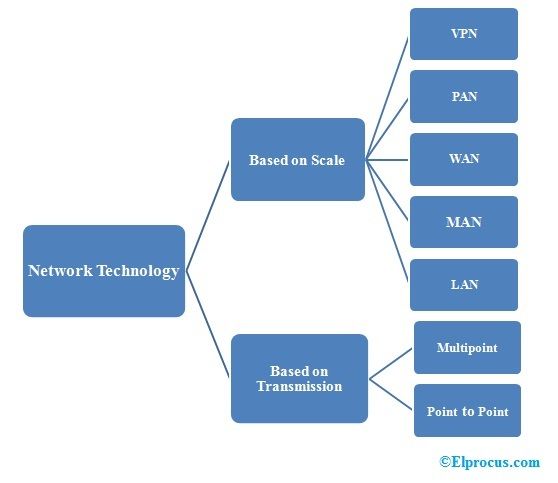

- Su emitteriu sujungta logika naudojama kaip logikos ir sąsajos technologija itin didelės spartos ryšio įrenginiuose, tokiuose kaip šviesolaidinių siųstuvų-imtuvų sąsajos, Ethernet ir ATM (asinchroninio perdavimo režimo) tinklai.

- ECL yra loginė šeima, pagrįsta BJT, kur jos didelės spartos veikimas gali būti pasiektas naudojant santykinai mažą įtampos svyravimą ir išvengiant tranzistorių judėjimo į prisotinimo sritį.

- ECL naudojamas kuriant ASLT grandines IBM 360/91.

- ECL išvengia sudėtinių tranzistorių naudojimo, naudojant vienpusį poslinkį i/p ir teigiamą grįžtamąjį ryšį tarp pirminio ir antrinio tranzistorių, kad būtų pasiekta keitiklio funkcija.

- ECL naudojamas itin didelės spartos elektronikoje.

Taigi, tai yra emiterio susietos logikos apžvalga arba ECL – grandinė, veikimas, savybės, charakteristikos ir programos. ECL yra pati greičiausia logikos šeima, pagrįsta BJT, palyginti su kitomis skaitmeninės logikos šeimomis. Jis pasiekia maksimalų greitį naudodamas nedidelį įtampos svyravimą ir išvengdamas tranzistorių judėjimo į prisotinimo sritį. Ši loginė šeima suteikia neįtikėtiną 1ns sklidimo delsą, o naujausiose ECL šeimose šis delsimas yra sumažintas. Štai jums klausimas, koks yra alternatyvus ECL pavadinimas?