Į skaitmeninis-analoginis keitiklis ( Dacianas , D / A , D2A arba Nuo D iki A ) yra grandinė, skirta skaitmeniniam įvesties signalui paversti analoginiu išėjimo signalu. Analoginis-skaitmeninis keitiklis (ADC) veikia priešingai ir analoginį įvesties signalą paverčia skaitmeniniu išėjimu.

Šiame straipsnyje mes visapusiškai aptariame, kaip veikia skaitmeninės į analoginę ir analoginę į skaitmeninę keitiklį schemos ir formulės.

Elektronikoje galime rasti nuolat kintančias įtampas ir sroves skirtingais diapazonais ir dydžiais.

Skaitmeninėse grandinėse įtampos signalas yra dviejų formų, arba kaip loginis aukštas, arba loginis žemas loginis lygis, kuris reiškia dvejetaines reikšmes 1 arba 0.

Analoginiuose ir skaitmeniniuose keitikliuose (ADC) įvestas analoginis signalas vaizduojamas kaip skaitmeninis dydis, o skaitmeninio analogo keitiklis (DAC) skaitmeninį dydį paverčia atgal į analoginį signalą.

Kaip veikia skaitmeniniai ir analoginiai keitikliai

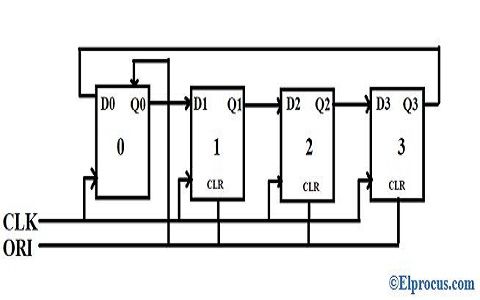

Skaitmeninis-analoginis konversijos procesas gali būti atliekamas naudojant daugybę skirtingų metodų.

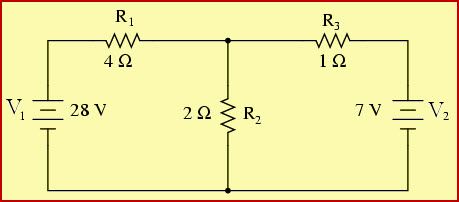

Vienam gerai žinomam metodui naudojamas rezistorių tinklas, žinomas kaip kopėčių tinklas.

Kopėčių tinklas suprojektuotas priimti įvadus, susijusius su dvejetainėmis reikšmėmis, paprastai esant 0 V arba Vref, ir tiekia išėjimo įtampą, lygią dvejetainio įėjimo dydžiui.

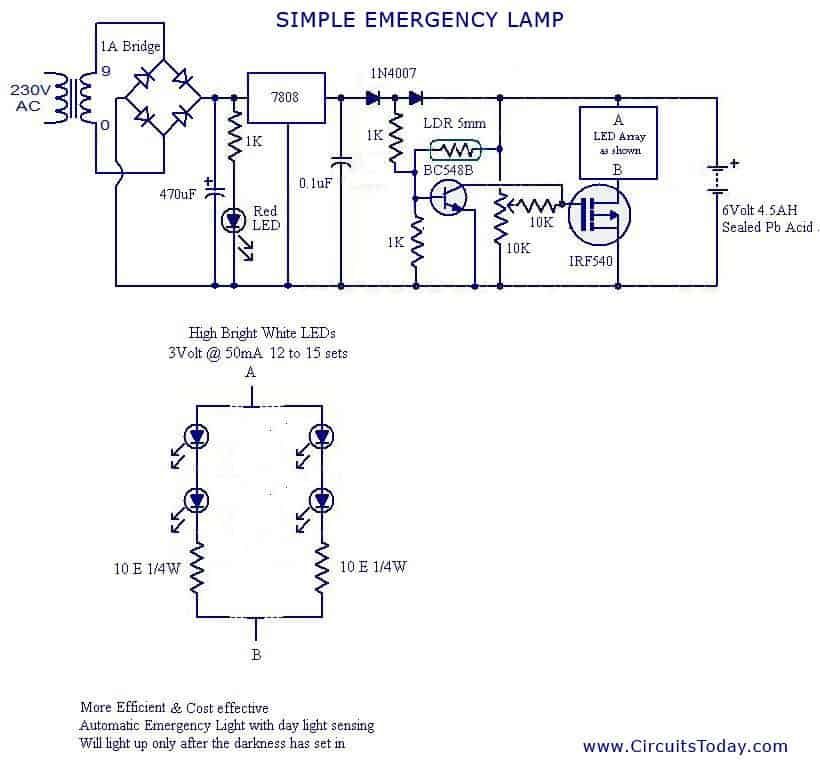

Žemiau pateiktame paveikslėlyje parodytas kopėčių tinklas, kuriame naudojamos 4 įvesties įtampos, kurios atspindi 4 skaitmeninių duomenų bitus ir nuolatinės įtampos išėjimą.

Išėjimo įtampa yra proporcinga skaitmeninės įvesties vertei, išreikštai lygtimi:

Išsprendę pirmiau pateiktą pavyzdį, gauname tokią išėjimo įtampą:

Kaip matome, skaitmeninis 0110 įvestisdukonvertuojamas į analoginę 6 V išvestį.

Kopėčių tinklo tikslas yra pakeisti 16 galimų dvejetainių dydžių

nuo 0000 iki 1111 į vieną iš 16 įtampos dydžių V intervalaisnuoroda/ 16.

Todėl gali būti įmanoma apdoroti daugiau dvejetainių įėjimų, įtraukiant daugiau kopėčių vienetų, ir kiekvienam žingsniui atlikti didesnę kvantavimą.

Reikšmė, tarkime, jei naudosime 10 žingsnių kopėčių tinklą, tai leis padidinti įtampos žingsnio kiekį arba skiriamąją gebą iki Vnuoroda/ du10arba Vnuoroda/ 1024. Šiuo atveju, jei mes naudojome etaloninę įtampą Vnuoroda= 10 V generuotų išėjimo įtampą 10 V / 1024 žingsniais arba maždaug 10 mV.

Taigi, pridėjus daugiau kopėčių pakopų, skirsime proporcingai didesnę skiriamąją gebą.

Paprastai už n kopėčių laiptelių skaičių, tai galima pateikti naudojant šią formulę:

Vnuoroda/ dun

DAC blokinė schema

Žemiau pateiktame paveikslėlyje parodyta standartinio DAC, naudojant kopėčių tinklą, vadinama R-2R kopėčiomis, blokinė schema. Tai galima pamatyti užrakintą tarp etaloninio srovės šaltinio ir srovės jungiklių.

Srovės jungikliai yra susieti su dvejetainiais jungikliais, sukuriant išėjimo srovę, proporcingą įvesties dvejetainiai vertei.

Dvejetainiai įėjimai perjungia atitinkamas kopėčių kojas, leidžiant išėjimo srovę, kuri yra svertinė dabartinės atskaitos suma.

Jei reikia, rezistorius galima prijungti prie išėjimų, kad rezultatas būtų interpretuojamas kaip analoginis išėjimas.

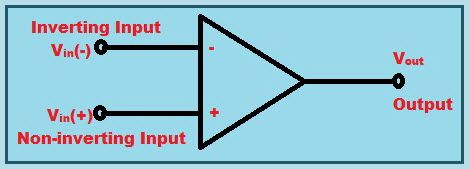

Kaip veikia analoginiai-skaitmeniniai keitikliai

Iki šiol mes diskutavome, kaip konvertuoti skaitmeninius į analoginius signalus, dabar sužinokime, kaip elgtis priešingai, ty konvertuoti analoginį signalą į skaitmeninį signalą. Tai galima įgyvendinti naudojant gerai žinomą metodą, vadinamą dvigubo nuolydžio metodas .

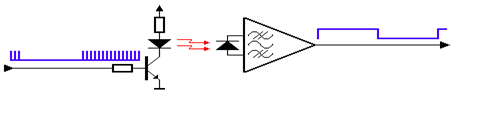

Šiame paveikslėlyje parodyta standartinio dvigubo nuolydžio ADC keitiklio blokinė schema.

Čia naudojamas elektroninis jungiklis norimam analoginiam įvesties signalui perduoti į integratorių, dar vadinamą rampos generatoriumi. Šis rampos generatorius gali būti kondensatoriaus pavidalo, įkrautas pastovia srove tiesinei rampai generuoti. Tai sukuria reikiamą skaitmeninę konversiją per skaitiklio etapą, kuris veikia tiek teigiamus, tiek neigiamus integratoriaus nuolydžio intervalus.

Metodą galima suprasti tokiu aprašymu:

Visas skaitiklio matavimo diapazonas nustato fiksuotą laiko intervalą. Šiuo laikotarpiu integratoriui įvestos analoginės įėjimo įtampos dėka palyginamojo įėjimo įtampa pakyla iki tam tikro teigiamo lygio.

Remiantis aukščiau pateiktos diagramos (b) skyriumi, parodyta, kad įtampa iš integratoriaus fiksuoto laiko intervalo pabaigoje yra didesnė už didesnę įėjimo įtampą.

Baigus fiksuotą laiko intervalą, skaičius nustatomas į 0, kuris paragina elektroninį jungiklį prijungti integratorių prie fiksuoto atskaitos įėjimo įtampos lygio. Po to integratoriaus išvestis, kuri yra ir kondensatoriaus įvestis, pradeda kristi pastoviu greičiu.

Šiuo laikotarpiu skaitiklis vis žengia į priekį, o integratoriaus išėjimas ir toliau krinta pastoviu greičiu, kol nusileidžia žemiau palyginamojo etaloninės įtampos. Dėl to palyginamoji išvestis keičia būseną ir paskatina valdymo logikos etapą sustabdyti skaičiavimą.

Skaitiklio viduje laikomas skaitmeninis dydis tampa skaitmenine keitiklio išvestimi.

Naudojant bendrą laikrodžio ir integratoriaus etapą tiek teigiamų, tiek neigiamų nuolydžių intervalais, gaunama tam tikra kompensacija laikrodžio dažnio dreifo kontrolei ir integratoriaus tikslumo riba.

Gali būti įmanoma pakeisti skaitiklio išvestį pagal vartotojo pageidavimus, tinkamai nustatant etaloninę įvesties vertę ir laikrodžio dažnį. Mes galime turėti skaitiklį kaip dvejetainį, BCD ar kitą skaitmeninį formatą, jei to reikia.

„Ladder Network“ naudojimas

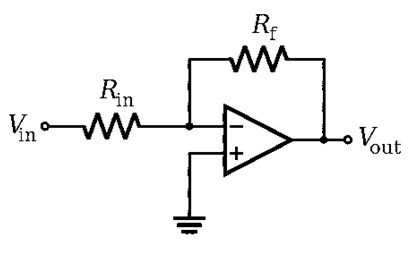

Kopėčių tinklo metodas, naudojant skaitiklių ir lyginamuosius etapus, yra dar vienas idealus būdas konvertuoti analogą į skaitmeninį. Taikant šį metodą, skaitiklis pradedamas skaičiuoti nuo nulio, kuris varo kopėčių tinklą, generuodamas pakopinę didėjančią įtampą, panašią į laiptus (žr. Paveikslą žemiau).

Procesas leidžia įtampai didėti kiekvienu skaičiavimo žingsniu.

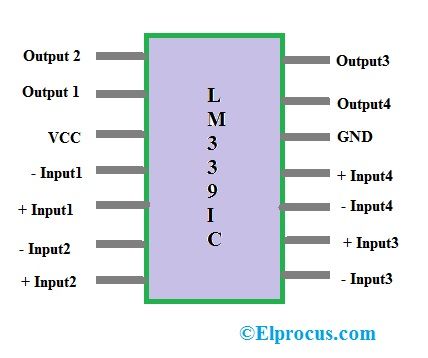

Palyginamasis stebi šią didėjančią laiptų įtampą ir lygina ją su analoginės įėjimo įtampa. Kai tik komparatorius pajunta laiptinės įtampą, einančią virš analoginės įvesties, jo išvestis paragina sustabdyti skaičiavimą.

Skaitiklio reikšmė šiame taške tampa skaitmeniniu analoginio signalo atitikmeniu.

Įtampos, kurią generuoja laiptų signalo žingsniai, pokyčio lygis nustatomas pagal naudojamų skaičiavimo bitų kiekį.

Pavyzdžiui, 12 pakopų skaitiklis, naudojant 10 V atskaitą, veiks 10 pakopų kopėčių tinklą, kurio žingsnio įtampa yra:

Vnuoroda/ du12= 10 V / 4096 = 2,4 mV

Tai sukurs 2,4 mV konversijos skiriamąją gebą. Laikas, reikalingas konversijai įvykdyti, nustatomas pagal skaitiklio laikrodžio greitį.

Jei 12 pakopų skaitikliui valdyti naudojamas 1 MHz takto dažnis, maksimalus laikas, reikalingas konversijai, būtų:

4096 x 1 μs = 4096 μs ≈ 4,1 ms

Mažiausiai konversijų, kurios gali būti įmanoma per sekundę, skaičius gali būti toks:

ne. konversijų = 1 / 4,1 ms ≈ 244 konversijos per sekundę

Veiksniai, turintys įtakos konversijos procesui

Atsižvelgiant į tai, kad kai kurioms konversijoms gali prireikti didesnės, o kai kurioms gali prireikti mažesnio skaičiavimo laiko, paprastai konversijos laikas = 4,1 ms / 2 = 2,05 ms gali būti gera vertė.

Tai duos vidutiniškai 2 x 244 = 488 konversijų skaičių.

Lėtesnis laikrodžio rodiklis reikštų mažiau konversijų per sekundę.

Konverterio, veikiančio su mažesniu skaičiavimo etapų skaičiumi (maža skiriamoji geba), konversijos lygis būtų didesnis.

Keitiklio tikslumą lemia kompartoriaus tikslumas.

Pora: Kaip apskaičiuoti ferito šerdies transformatorius Kitas: Ultragarso kuro lygio indikatoriaus grandinė